介绍了锁相环路的基本原理,分析了集成锁相环芯片ADF4106的工作特性,给出了集成锁相环芯片ADF4106的一个应用实例,为高频频率合成器的设计提供了很好的思路。

关键词:ADF4106,锁相环,频率合成器,环路滤波器?

1 引言

在无线通信领域中,高性能频率源是通信设备、雷达、电子侦察和对抗设备、精密测量仪器的核心部件。现代通信系统对频率源的精度、分辨率、转换时间及频谱纯度等提出了越来越高的要求,性能卓越的频率源均通过频率合成技术来实现。本文所讨论的锁相环频率合成技术是基于锁相环路的同步原理,由一个高准确度、高稳定度的参考晶体振荡器,综合出大量离散频率的一种技术。锁相环频率合成器是一种相位锁定装置,是一种频率稳定度较高的离散间隔型频率信号发生器。

2 锁相环频率合成器的基本原理

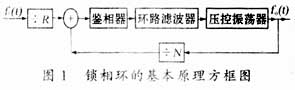

锁相环是频率合成技术的基础。锁相环路(PLL)通常由鉴相器(PD)、环路滤波器(LP)、压控振荡器(VCO)和可变程序分频器组成。

锁相环路是一个相位误差控制系统,它比较输入信号与压控振荡器输出信号之间的相位差,产生一个对应于两个信号相位差的误差电压,该误差电压经处理后去调整压控振荡器的频率(相位)。当环路锁定时,输入信号与压控振荡器输出信号频差为零,相位差不再随时间变化,此时,误差控制电压为一固定值,压控振荡器输出频率与输入信号频率相等,即fo=fr。锁相环路的这一特点,使它在自动频率控制中得到应用,以实现精确的频率控制。环路在锁定时要得到一定的控制电压,则鉴相器必须有一个非零的输出,即,环路作用必须有相位差,相位差维持着两信号的同步,使输出信号频率稳定。

锁相环基本原理方框图如图1所示。?

鉴相器又称比相器,对输入信号与环路输出信号的相位进行比较, 产生误差控制电压;环路滤波器滤除误差电压中的高频分量和噪声,以保证环路所要求的性能,增加环路的稳定性;压控振荡器的振荡频率受环路滤波器输出电压的控制,使压控振荡器输出信号频率向输入信号频率靠拢,两个信号间的相位差减小。可变程序分频器的作用是使压控振荡器的输出频率经分频后再与参考频率进行相位比较,从而产生误差控制电压,并以误差控制电压来调整压控振荡器的相位。

锁相环路对高稳定度的参考振荡器(通常是晶体振荡器)锁定,环路串接可编程的程序分频器,通过编程改变程序分频器的分频比R、N,从而获得N/R倍参考频率的稳定输出。频率合成器输出频率fo与晶体振荡器参考频率fr的关系为

![]()

其中,R是固定分频比,N是程序(可变)分频比,fr是晶振输出的参考频率,fo是频率合成器的输出频率。

3 基于ADF4106的锁相环频率合成器的设计与实现

3.1 集成锁相环芯片ADF4106介绍

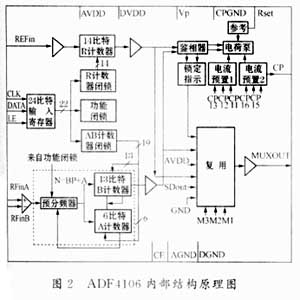

ADF4106是美国ADI公司最新生产的锁相环芯片,它是一种频率上限高、性能好的集成数字锁相环频率合成器芯片,在一块很小的芯片中集成了锁相环频率合成器的多种重要部件,只需再合理搭配上一、二块集成电路和少量的外围电路,即可构成一个完整的低噪声、低功耗、高稳定度的可靠性很高的频率合成器,设计应用简单灵活,且易于减小系统体积。ADF4106的内部结构原理图如图2所示。?

集成锁相环芯片ADF4106具有较高的工作频率,最高达到6.0GHz,它主要应用于无线发射机和接收机中,为上下变频提供本振信号。该芯片主要由低噪声数字鉴相器,精确电荷泵,可编程参考分频器,可编程A、B计数器及双模前置分频器(P/P+1)等部件组成。数字鉴相器用来对R计数器和N计数器的输出相位进行比较,然后输出一个与二者相位误差成比例的误差电压。鉴相器内部还有一个可编程延迟单元,用来控制翻转脉冲的宽度,这个翻转脉冲保证鉴相器的传递函数没有死区,因此,降低了相位噪声和参考杂散。精确电荷泵采用可编程电流设置完成输出。可编程参考分频器实际上是一个14bit的R计数器,主要完成对外部恒温晶振进行分频,分频比的范围是1至16383,从而得到参考频率。可编程A、B计数器及双模前置分频器(P/P+1)共同完成主分频比N(N=BP+A), 双模前置分频器(P/P+1)也是可编程的,P的取值有几种模式:8/9,16/17,32/33,64/65。

ADF4106的最大特点就是它的极高的工作频率,使得许多高频系统的倍频装置得以精简,还简化了系统结构,降低了功耗和设备成本。因此,它在高频电路系统中得到广泛应用。

3.2 ADF4106应用实例

以ADF4106为核心,选择适合应用需要的外部压控振荡器,设计相应的环路滤波器,即可构成低噪声、低功耗、高稳定度的频率合成器。

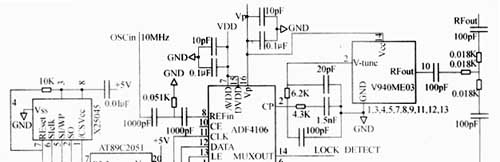

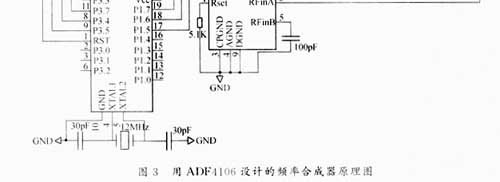

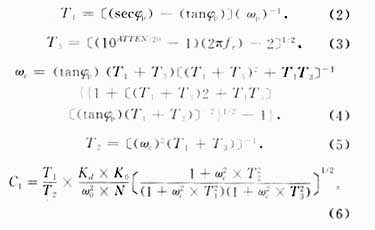

图3是某发射机中频率合成器的一个应用实例,其工作频率范围为5.4GHz~5.8GHz。在该频率合成器中,外部高精度高稳定的10MHz参考时钟经50Ω的匹配电阻,接到ADF4106的参考时钟输入端(REFin),经内部参考分频器(除10)后得到1MHz的参考频率间隔。ADF4106内部电荷泵的输出驱动环路滤波器采用三阶无源低通滤波器,参数设置:相位裕量φp=45°,鉴相器灵敏度Kd=2.5mA,压控振荡器灵敏度?K0=80MHz/V, 环路带宽ωp=50Hz, 参考频率间隔FREF=1MHz,参考分频比R=10,主分频比N=RFOUT/FREF=5800,滤波器的附加衰减ATTEN=10dB。

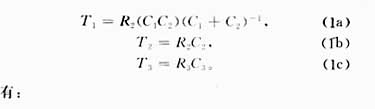

由环路滤波器设计原理,根据下面的公式, 定义时间常数为:

可以计算出C1,C2,R2,并取标称值:C1=100pF,C2=1.5nF,R2=4.3kΩ,取R3=6.2kΩ, C3=20pF。

环路滤波器的输出去驱动压控振荡器,在这里,压控振荡器选用ZCOMM公司的V940ME03,它具有很高的振荡频率;压控振荡器的输出又反馈到ADF4106的射频输入端,形成环路,进而推动射频输出端。在V940ME03的RFout端,整个电路的射频输出端及ADF4106的射频输入端,加了一个T型电路,主要用来提供50Ω的阻抗匹配。

ADF4106的供电电压VDD为3V,Vp和VCO的供电电压VCC为5V,均采用稳压块供电输出。需要特别注意的是,VDD一定不能超过Vp,否则,会损坏器件。

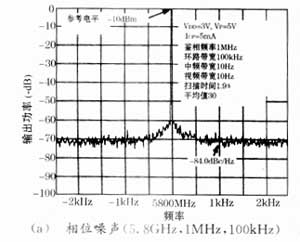

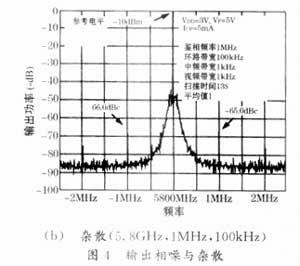

本例中,相噪、杂散等指标均达到了设计手册中如图4所示ADF4106的标准,其中,测量结果的典型值是相位噪声为-81dBc/Hz@1kHz,杂散优于-62dBc。

4 结束语?

由于用ADF4106在高频频段设计的频率合成器应用于许多高频系统,精简了倍频装置,简化了系统结构,降低了功耗和设备成本,因此,它在高频电路系统如宽带无线接入、仪器仪表、无线局域网、无线电射频基站中得到了广泛应用。

更多锁相环知识请访问 http://www.elecfans.com/zhuanti/PLL.html

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)