图像处理系统的一个关键问题就是数据量庞大,数据处理相关性高,实时实现比较困难。即使采用高速单片机也无法满足实时处理的需求,而DSP芯片则具有速度快,信号处理功能强大,实时性好等特点,因此,将DSP用于图像处理可使这一难题得到较好的解决。

1 系统构成

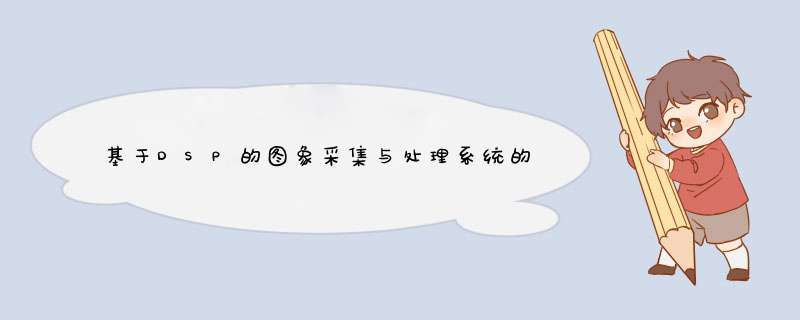

本系统采用基于CameraLink接口的图像输出相机。DSP采用TI的TMS320C6711,这是一种高性能DSP处理器,其工作频率为150 MHz,最大处理能力高达900MFLOps,该DSP既可满足高速处理要求,又可满足高精度运算时的浮点要求。

本图像处理系统主要包括图像采集模块(由MDR26连接器DS90CR288A和IDT72V283组成)、图像处理模块(由DSP器件TMS320C6711、SDRAM图像存储器和FLASH程序存储器等组成)以及图像输出系统(USB和FPGA)等。该系统的构成原理框图如图1所示。其基本工作过程是将高速CCD相机采集到的图像数据通过电缆接入MDR26连接器,然后再接入LVDS线路接收器DS90CR288A以将其恢复成并行TTL信号,同时分离出8位图像数据和3个控制信号。而同步FIFO作为数据缓存则不会造成数据的丢失。当其数据达到半满时,HF有效,此时可触发DSP中断以通知DSP将FIFO中的数据取走,并开始进行数据处理。DSP与USB的数据传递建立在消息和中断信号基础上,当DSP或USB任何一方有数据发送时,发送方先将数据和消息送到FPGA,然后用I/O脚触发中断至接收方,接收方接到中断后再到FPGA中读取消息,然后根据消息的内容读取数据。

本系统设计充分利用了TMS320C6711中EDMA的优势,并用EDMA来进行整个系统的数据传输。由于EDMA可以进行背景 *** 作,因而其整个采样和输出过程基本不影响 *** 作。同时,也利用了TMS320C6711的二级缓存结构,再加上系统外围采用高速的数据存储器芯片,因而大大提高了整个系统的处理速度。

2 图像采集与处理

2.1 Camera Link技术

Camera Link技术的核心是美国NS(NaTIonalSemiconductor)提出的一种高速数据传输方法—Channel Link传输方法技术,该技术主要用于数字图像数据的高速传输。该技术采用LVDS信号模式,但比先前的RS644传输方法具有明显的优点。LVDS(Low Voltage DifferenTIal Signaling)是最近发展起来的一种利用低电压差分信号模式的传输技术。LVDS信号是以+1.2 V为基准的300 mV差分形式,其低电压摆幅差分模式具有高速传输数据时交叉干扰小,EMI干扰小等特点。ChannelLink采用LVDS方式传输数据,它将28位数据转换成串行方式在4对线路上进行传输,然后再用另外一对线路传输时钟信号,其最高传输率可达2.38 Gb/s。传输距离可达10 m。NS的LVDS发送器DS90CR287可用于完成并行TTL/CMOS信号到LVDS信号的转换,LVDS线路接收器DS90CR288则用来将LVDS信号还原成并行TTL/CMOS信号。

2.2 TMS320C6711 DSK简介

本系统采用美国TI公司的TMS320C6711DSK(DSP Starter Kit)开发工具。这是由TI公司提供的一套独立的C6000开发实验平台,这种开发工具集成了一些基本的应用电路,它既可以帮助用户评估和开发C6000系列DSP的功能,也可以作为DSP初学者的学习工具。它的硬件由6711 DSP构成,主频为150 MHz,凭借其二级高速缓存及VLIW (very long instruction word)架构,每秒可执行900万次浮点运算(MFLOPS)。DSK可以提供双时钟,通过设定可使CPU工作在150 MHz,而使扩展存储器接口(EMIF)工作在100 MHz。 DSK上设计有16 M字节/100 MHz的SDRAM和128 K字节的ROM。SDRAM由TMS320C6711为其产生所需的控制信号和刷新信号。最大刷新周期可达15.625 ms。HPI接口可通过并口连接所有的DSP存储空间,并有子卡接口所需的存储器和外围连接接口及嵌入式JTAG仿真功能。

2.3 图像采集与处理接口设计

根据CameraLink标准,CCD输出图像数据经Camera link后,可由LVDS线路接收器DS90CR288将其恢复成并行的TTL/CMOS信号,并分离出8位图像数据和3个控制信号(LVAL,DVAL,STROBE)接人同步FIFO(IDT72V283),再通过DSP的外部存储器接口(EMIF)接入TMS320C6711DSK开发板进行图像数据处理。其具体的图像采集电路原理图如图2所示。

3 图像输出系统

3.1 USB芯片AN2131QC

USB芯片选用CYPRESS半导体公司的EZUSB(AN2131QC)芯片,AN2131 QC具有一个USB接口、8位数据线和16位地址线,以及3个8位I/O端口,其片内带有增强型8051核,该8051核与传统8051的区别在于其速度较快。传统的8051标准指令周期是12个CLOCK,而在这里只需要4个CLOCK,因而大大提高了指令执行的时间。由于其带有增强8051核,故可以将固件储存在主机上,每次上电时,再将固件调用到芯片的RAM存储器单元,这样可使固件升级非常容易。另外,CYPRESS公司还提供了一个不需要修改就可以使用的驱动程序ezusb.Sys,这个驱动程序允许任何传输类型与EZ-USB芯片构建的系统进行通信。CPU的时钟频率为24 MHz,使用RAM作为程序存贮器,其8051程序代码及设备描述表可以每次从主机中下载。

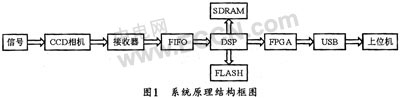

3.2 图像输出接口设计

TMS320C6711与AN2131QC采用并口方式进行通讯。DSP为32位处理器,其并行接口数据线为32根,而AN213 I QC的并行口为8位,若将DSP32根数据线中的8根数据线直接与USB并口相连,则DSP传送一个32位数据需进行4次 *** 作,这显然会影响系统的效率。因此,可采用8位/32位数据线转换和数据缓冲设备来将两者相连。考虑到性能价格等因素,本设计采用FPGA作为两者之间的缓冲设备,实现从DSP到USB数据传输缓冲以及32位数据线转8位数据线功能。FPGA采用X ilinx公司SpartanIIE系列的XC2SSOE芯片作为转换器。其图像传输电路原理图如图3所示。

4 系统软件设计

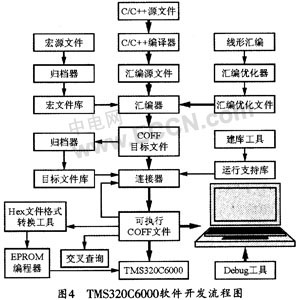

4.1 DSP的软件开发

TMS320C6000软件开发的一切过程都可在CCS集成环境下进行,包括项目的建立、源代码的编辑以及程序的编译和调试。图4所示是TMS320C6000的软件开发流程图。其中黑体部分是开发C代码的常规流程,其它功能可用于辅助和加速软件开发过程。

该CCS能对用户开发的源代码进行优化。目的是缩短代码长度并提高代码执行效率。其中,C优化器对C源代码进行优化,所进行的优化包括针对C代码的一般优化和针对C6000的优化,如重新安排语句和表达式、把变量分配给寄存器、打开循环和模块级优化(把若干个文件组成1个模块进行优化)等。C优化器完成的最重要的优化处理是软件流水(software pipeline)。软件流水是专门针对循环代码的一种优化技术,利用软件流水可以生成非常紧凑的循环代码,这也是C6000的C编译器能够达到较高编译效率的主要原因。

汇编优化器是C6000代码产生工具内极具特色的一部分。它在DSP业界首创了对线性汇编代码自动进行优化的技术。线性汇编语言是为简化C6000汇编语言程序的开发而设计的,它不是独立的编程语言。它可用用户编写的线性汇编代码作为输入,同时产生一个标准汇编代码作为输出。与C6000的标准汇编语言相比,采用线性汇编不需要考虑并行指令安排、指令延迟和寄存器,而由汇编优化器自动完成,其所产生的代码效率可以达到人工编写代码效率的95%-100%,同时还可以降低编程工作量,缩短开发周期。

C6000程序的调试和仿真有两种模式:软件仿真和硬件仿真。软件仿真时,其程序的执行完全靠主机上的仿真软件模拟,程序单步或者运行的结果都是仿真软件“计算”出来的。而硬件仿真需要目标板。仿真程序利用开发系统将代码下载到DSP,程序是在芯片上直接运行的。仿真软件只是把运行结果读出来显示。软件仿真无需目标板就可以开始软件编程,但仿真速度较慢,而且无法仿真某些外设的功能。硬件仿真的优点是仿真速度快,仿真结果与实际结果一致。

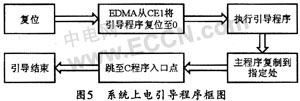

4.2 系统的上电引导

C6711的引导装载方式有三种:一是无引导,二是ROM/FLASH引导,三是主机引导。本设计采用FLASH引导。根据DSK开发板上EMIF与FIASH硬件电路连接设计的引导程序如图5所示。

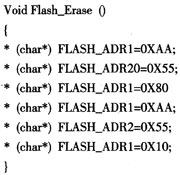

(1)FLASH存储器的擦除

擦除FLASH存储器的关键源代码如下:

至此FLASH内部地址已经映射到C6711的CE1空间,其开始地址为 0X90000000H,因此其FLASH_ADR1,FLSH_ADR2的定义如下:

#define FLASH_ADR1 0X90000555

#define FLASH_ADR2 0X900002AA

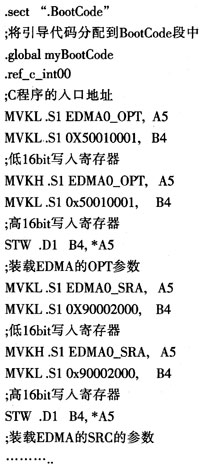

(2)汇编源代码文件

本引导代码的主要功能是将用户程序段从FLASH复制到DSP内部RAM中。然后再跳转到程序的入口处开始执行主程序。这里采用的是EDMA快速实现DSP存储空间数据搬移的方式。基于EDMA传输参数的设置方法如表1所列。其核心引导程序如下:

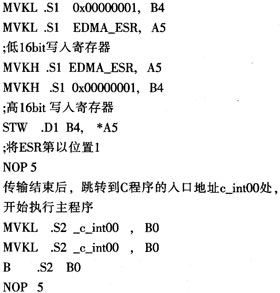

启动EDMA复制主程序段:CPU可以通过写事件置位寄存器(ESR)启动一个EDMA通道,ESR中某一位写1时,将强行触发对应的事件。程序如下:

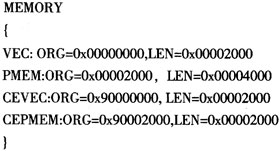

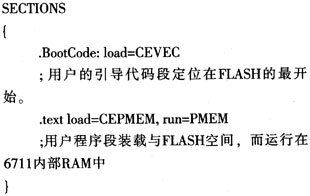

(3)链接命令文件

系统中的链接命令文件(boot.cmd)如下:

VEC,PMEM代表内部RAM的两个存储空间,而CEVEC,CEPMEM代表FLASH内的两块存储空间,对目标文件中各段的加载地址和运行地址可在SECTIONS段实现:

引导装载是设计DSP系统所必需的过程。本设计采用EDMA方式来实现程序的快速搬移,故可在自制的PCB板上正确地实现脱机运行。

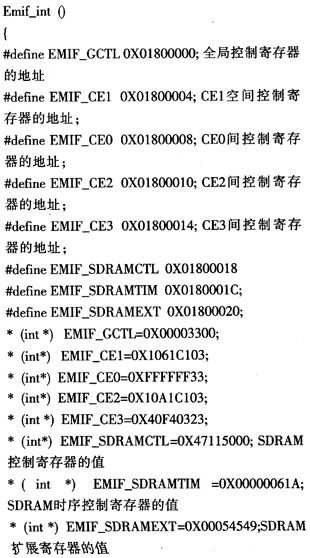

(4)对DSP寄存器的设置

只有对相应的寄存器实现EMIF初始化,DSP才能访问外部存储器的数据,其源代码如下:

5 结束语

本文介绍了为了在线线圈直径的测量而开发线阵CCD图像采集和处理设备的具体方法,该系统利用TI公司的高性能浮点DSP-TMS320C6711实现了对dalsa公司的Piranha2 P2—2x Camera输出数据的采集与处理。给出了一种通用的实时图像处理系统,并详细讨论了系统的具体结构。在该系统中运行一些基本的图像处理(锐化,平滑,边缘检测)和压缩算法(JPEG,H.263),都能达到实时处理的目的。但在实际应用中,由于要求进行连续采集与处理,最好能采用多个DSP并行工作方式。若物体的运动速度更快或图像处理更复杂时,还应采用性能更强的DSP(如TI的64X系列DSP或采用多个DSP并行处理)。另外,在DSP与USB通讯设计中引人FPGA可使系统的设计更加灵活,同时也可为系统以后的扩展提供方便。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)