电子发烧友网核心提示:随着信息技术的发展以及数字集成电路速度的提高,实时处理大量数据已经成为现实,但在一些特殊条件下,无法实时传输数据,必须使用存储测试方法。该方法是在不影响被测对象或在允许的范围下,将微型存储测试系统置入被测体内,现场实时完成信息的快速采集与存储,并回收存储器,由计算机处理,再现被测信息的一种动态测试技术。实际应用中,由于在不同的条件下对采样速率和采样精度的要求有所不同,系统的实现方法也各有特点。为了增加系统数据回收的可靠性,本文介绍了基于双备份存储的数据采集存储系统的设计与实现方法。

1 技术要求

在某飞行体遥测系统中,为了获取飞行体的参数,需要设计一种数据采集存储系统,要求实现对23路模拟信号的采集、编帧存储。要求输入信号电平为0~5 V,系统总采样率为245.76 kHz, 记录时间不小于500 s,对速变信号的采样率为5.12 kHz,缓变信号的采样率为160 Hz, 23路模拟量信号输入中包括9路速变信号和14路缓变信号。

2 整体方案的设计

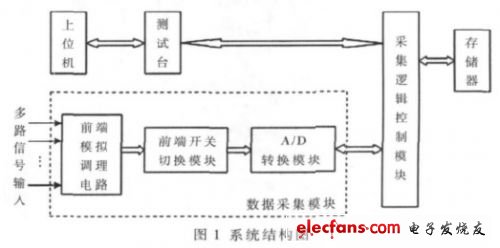

信号采集存储系统是基于双备份的数据存储器设计而成,整个系统以FPGA为核心控制器,控制数据的采集、编帧存储。系统结构如图1所示。

2.1采编器电路的设计

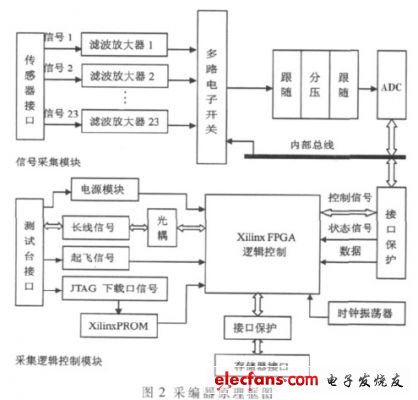

采编器主要完成对各种被测信号的采集,并对数据进行实时编码、逻辑控制和实时存储控制,分为速变、缓变信号采集模块和采集控制模块,两者通过内部总线相连。

速变、缓变信号采集模块主要完成23路输入模拟信号的调理、选择、A/D采集等功能,包括输入接口电路、滤波跟随电路、模拟通道切换电路、信号调理电路等。

采集控制模块完成模拟信号的A/D采集控制、编帧、内部时序控制等功能,包括长线接口电路、控制电路、存储器接口电路、帧结构下载电路等。

采编器的主控器件采用XC2S100E型现场可编程门阵列(FPGA),该器件体积小、功耗低、内部延时小,全部控制逻辑由硬件自动完成,编程配置灵活,可实现程序的并行执行,因而可大大提高系统的工作性能。该采编器的电压采集范围为0~+5 V,采集精度不低于0.1%.由于FPGA本身不具备A/D转换模块,因此各通道的模拟信号分别经信号调理电路后,由模拟多路开关ADG506选择模拟通道,再经外部高速AD7667实现A/D转换,转换的数据在FPGA内编帧后输出到存储器中。具体的每帧数据由各路模拟信号和帧标记FDB1 8540组成。采编器的电源由电源模块提供的5 V电压经TPS70351调理后产生。

采编器电路框图如图2所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)