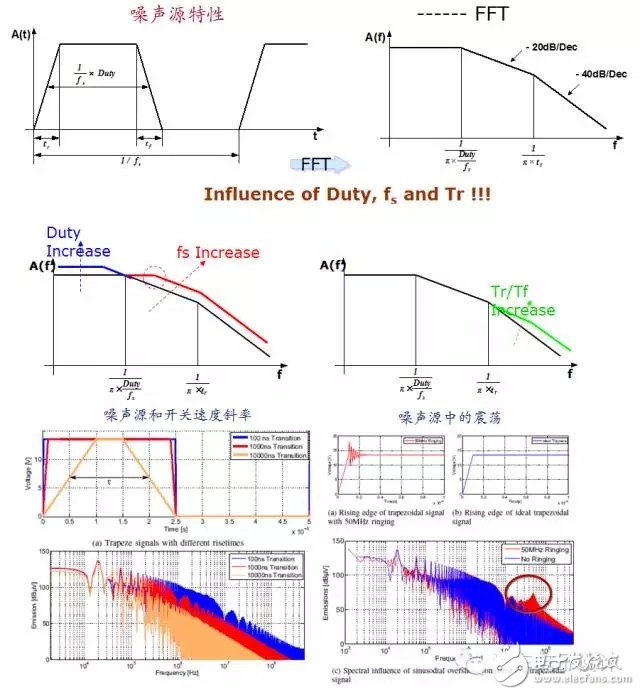

1)DCDC噪声源特性

DCDC的噪声的影响三个参数主要为:

占空比Duty:占空比上升导致噪声幅度上升

开关频率Fs:是的噪声衰减变在频谱上延伸了,开关频率一般我们可以分为几个大类

20~100Khz:电感较大引起的成本、尺寸基本让低频设计慢慢不是一种选择。

100~550Khz:主要的选择选择

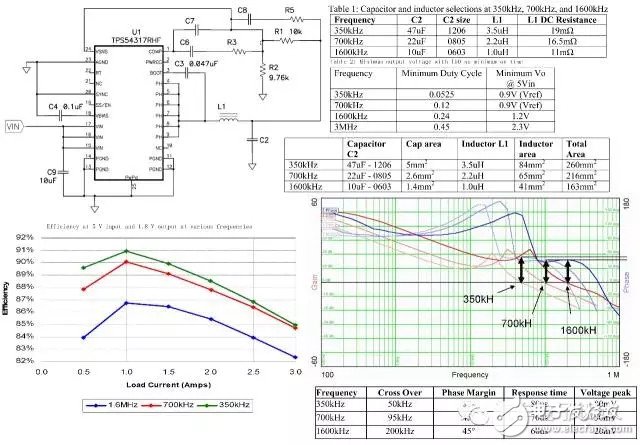

开关频率主要对电感大小、效率、RE/CE的特性影响比较大

上升时间Tr

备注:开关频率的影响其实很大,不仅仅是EMC的效果,在不同的案子里面可以得到不同的影响关系,如《Choosing the opTImum switching frequency of your DC/DC converter》所示:

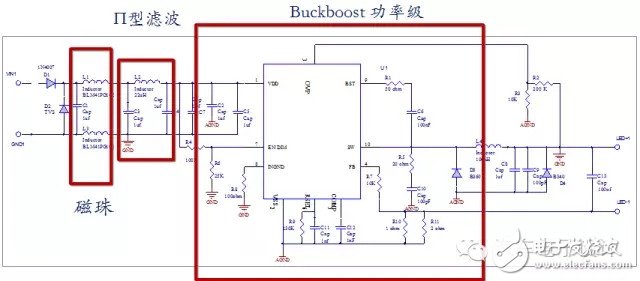

2)如下面的案子所示

2.1)这是一个典型的BuckBoost的电源电路,没有病必需要过CISPR25 Class 3

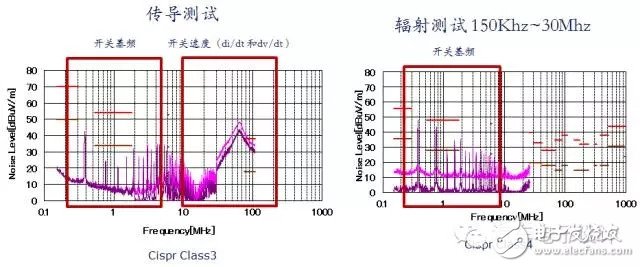

2.2 初测结果

2.3 整改措施

2.3.1 原理分析

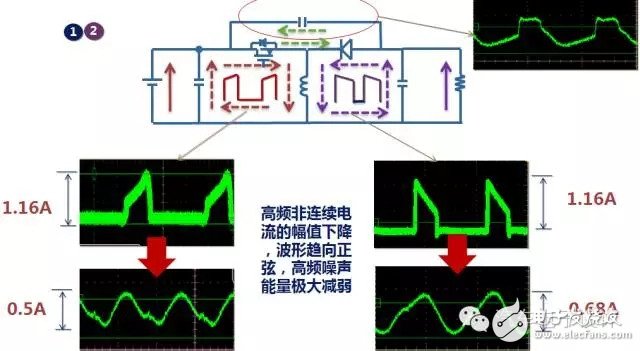

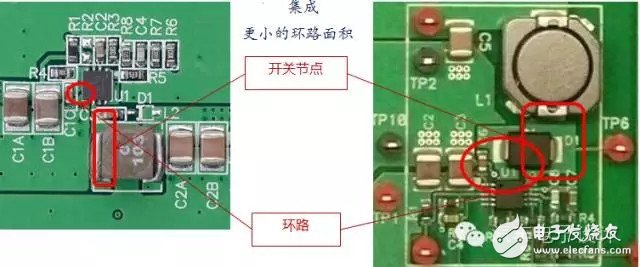

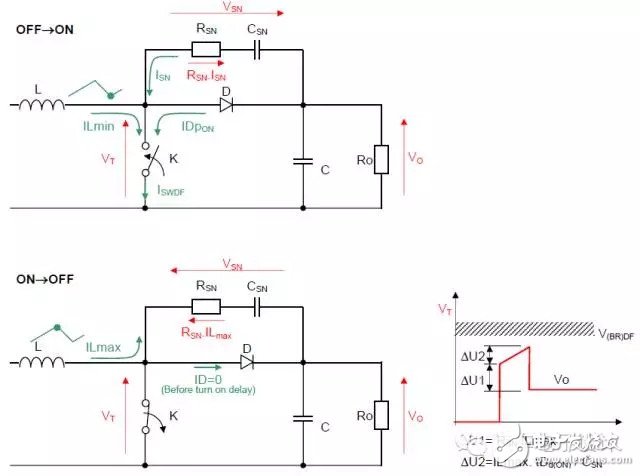

两个开关环路中含有非连续的大电流环路是最主要的噪声源

增加Vin和Vss电容可以减少高频环路的电流

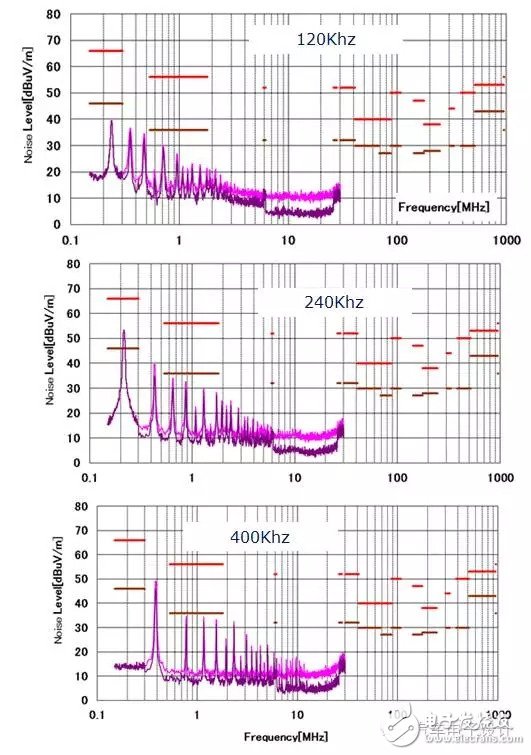

2.3.2 频率选择

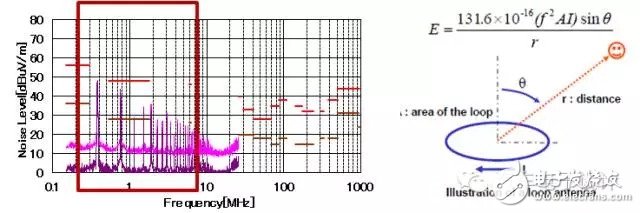

噪声分量和电流大小,环路面积和频率成正比,和距离成反比

以下依次为不同频率的效果对比(120、240和400Khz),深紫色为抖频的效果

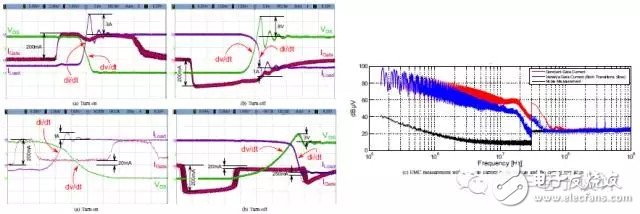

2.3.2 开关速度的优化

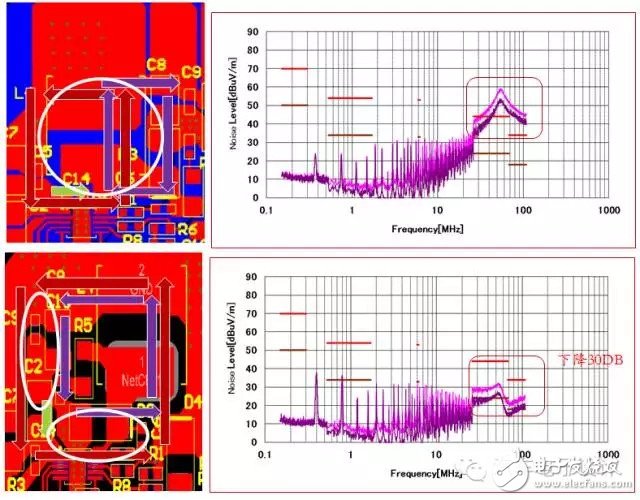

2.3.3 布局优化影响

在布局上尽可能将C14(Vin-Vss电容)放在续流二极管和MOSFET边上减少高频环路面积

以下是实物照片

补充一些相关的材料,除开芯片厂家的努力,我们能加入的设计手段主要包括:

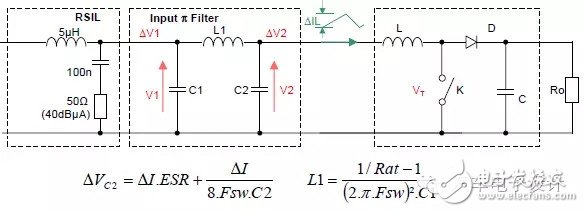

1)输入滤波优化

RSIL filter 5μH 100nF 50Ω

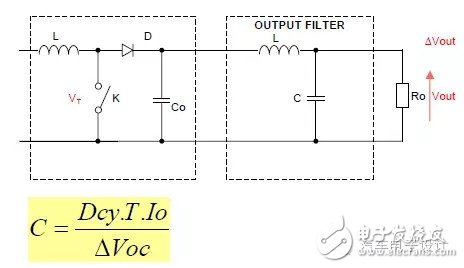

2)输出滤波优化

3)Snubber电路

小结:

1)感谢建宇兄的案例总结,我们可以定量和定性的看这些参数的选择对实际试验的结果

2)这个的设计,需要打通原理、计算、功能试验和实际验证的环路

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)