C240x系列DSP是面向数字控制系统的新一代数字信号处理器。该控制器集实时处理能力和控制器设计功能于一身,为控制系统应用提供了一个理想的解决方案。其内部的哈佛结构使数据空间和程序空间分离,独立的数据总线和程序总线允许程序数据同时 *** 作;专用的硬件乘法器极大提高了运算速度;具有独特的逆寻址方式,能高效地进行快速傅里叶变换运算;指令系统采用流水线 *** 作,减小了指令周期;采用内存映射方式管理I/0,能灵活方便地扩充外围电路。

1 主电路硬件设计

1.1 系统总体设计

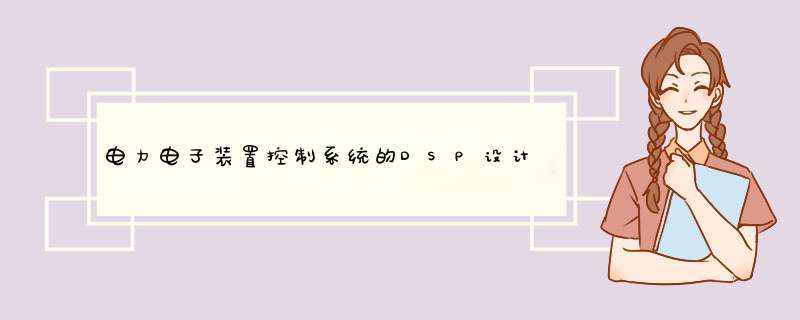

一般电力电子装置控制系统的总体结构如图1所示。详细介绍各单元的功能与硬件电路。

1.2电平转换

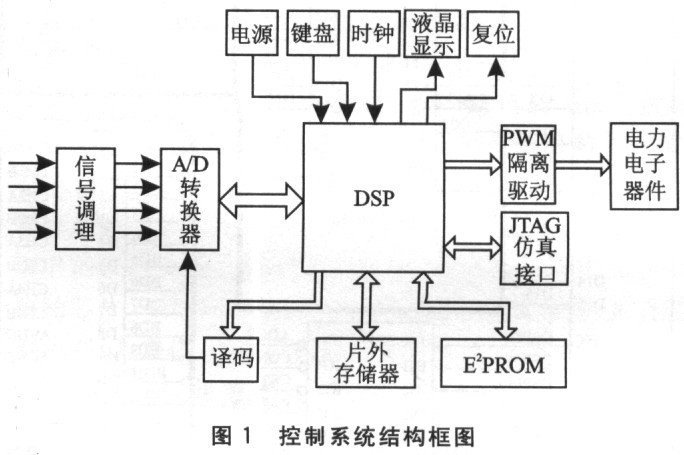

TMS320LF2407a(以下简称2407a)采用3.3V电,减小了芯片功耗;但常用直流电源为5V,因此必须考虑电平转换问题。一种方法是直接采用可调直流电源获得3.3V电压,但这样很难保证电源电压的稳定性,影响DSP的正常运行。另一种方法是采用专门的电源芯片,将5 V电压降为3.3 v。TPS76833、TPS76HD318、MAX604为常用的电平转换芯片。图2为采用MAX604实现电子转换的电路。并联于电源与地之间的电容起稳压作用。

1.3 时 钟

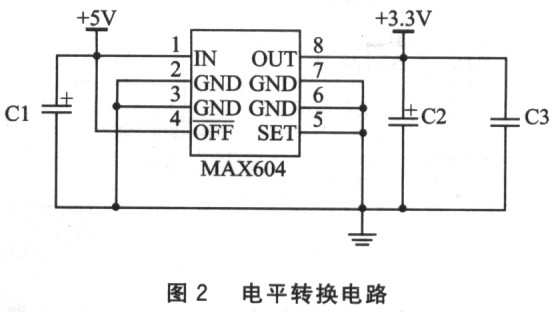

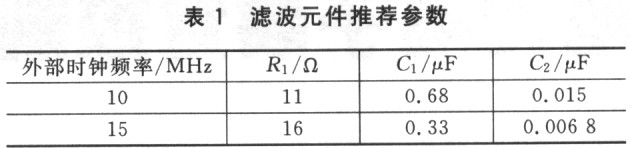

与一般微处理器不同,C240x系列DSP利用挂接在片内外设总线上的锁相环时钟模块(PLL)合成系统需要的各种时钟信号(CPU时钟、系统时钟、模拟时钟和看门狗时钟)。外部时钟信号经PLL倍频后合成系统时钟频率。如图3所示,外部时钟信号由lO MHz晶振提供,通过系统控制和状态寄存器(SCSR1)设置4倍频因子后,2407a DSP以最大时钟频率(40MHz)工作。通过检查DSP时钟输出引脚(CLK0UT)的频率,可以判断DSP芯片是否已开始正常工作。PLL模块使用外部滤波器回路来抑制信号抖动和电磁干扰。滤波器回路由PLL接在滤波器输入引脚PLLF和PLLF2之间的电阻Rl和电容Cl、C2组成。电容Cl、C2必须为无极性电容。在不同的振荡器频率下,R1、Cl、C2的取值不同,常用的参数组合如表l所列。PLL模块的电源引脚PLLVCCA分别通过磁珠和0.1μF的电容与数字电源引脚VDD和数字地引脚VSS连接,构成低通滤波电路,保证时钟模块的可靠供电。

1.4 片外存储器

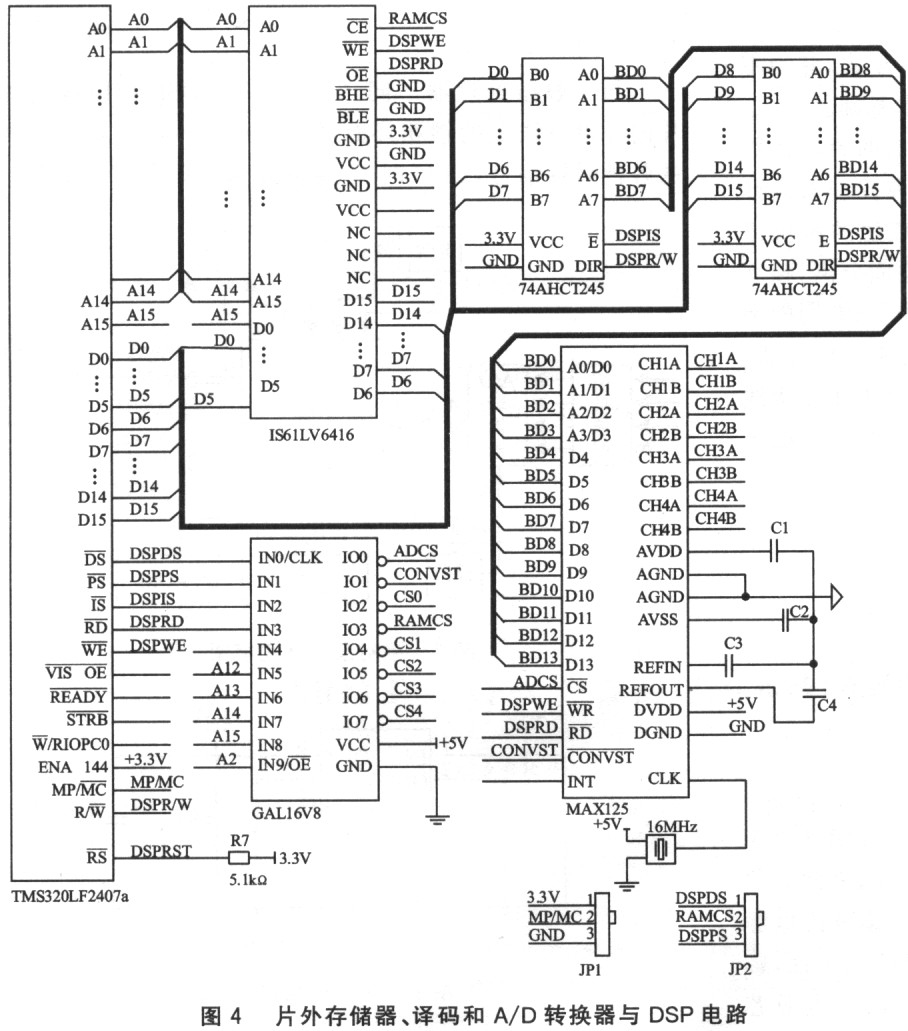

2407aDSP可以访问的程序存储空间为64K字,根据MP/MC引脚的电子决定其配置方式。当MP/MC为低电平时,片内Flash存储空间使能,地址范围是0000h~7FFFFh,8000h~FFFFh的地址留给外部程序存储器。当MP/MC为高电平时,片内Flash被禁止,64 K字存储空间全部位于外部程序存储器中,即只能从片外存储器中读取数据,使得仿真调试时通过仿真器对程序修改比较容易。2407a DSP有64K的16位数据存储器空间,32 K字的内部存储器地址范围是0000h~7FFFh,包括存储器映射寄存器、DARAM和外设映射寄存器。另外,地址范围是8000h~FFFPh的32 K字留给外部数据存储器空间。片外存储器的选择主要考虑电压、容量、速度等指标。本文采用工作电压3.3 V,容量64K×16位,访问时间15 ns的高速静态RAM,IS6lLV6416-15T作为片外存储器。如图4所示,片外存储器的数据、地址线分别与DSP对应相连;输出使能引脚OE和输入使能引脚WE分别与DSP的读选通DSPRD相连。仿真调试时,用跳线把片选引脚DSPWE与DSP的程序空间选通引脚CE相连,当外部程序存储器用。程序烧写到片内Flash后,把片选引脚CE与DSP的数据空间选通引脚DSPDS相连,当外部数据存储器用。

1.5 译码电路

GAL器件是在PAL器件基础上发展起来的逻辑器件。作为一种可电改写、可重复编程、可加密的新型可编程逻辑器件,它具有速度快、容量大、功耗低而且设计灵活的优点。本文采用GAL16V8D作为译码芯片,输入信号有DSP读使能、写使能、数据空间选通、程序空间选通、I/O空间选通和高5位地址线,通过逻辑组合后,输出A/D等外围器件的片选信号。

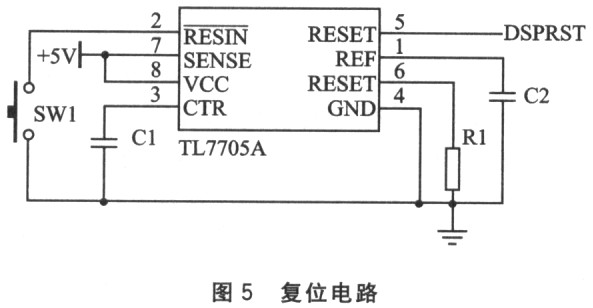

1.6 复位电路

2407aDSP有两种复位源,外部复位引脚复位和程序监视定时器(看门狗)复位.复位引脚(133)是一个I/O脚,正常状态通过上拉电阻接电源。当有内部复位事件发生时,该引脚被驱动为低电平输出方式,给系统中其他芯片提供复位信号;当有外部复位事件发生(手动复位、上电复位、欠电压复位等)时,该引脚为输入方式,同时将复位中断向量0000H加载到程序计数器PC中,使程序重新开始执行。TL7705A具有处理上电复位、欠电压检测复位、手动复位的功能.本文用它来实现外部复位信号管理功能,其复位信号输出引脚与DSP的复位引脚相连,电路如图5所示。

1.7 串行E2PROM

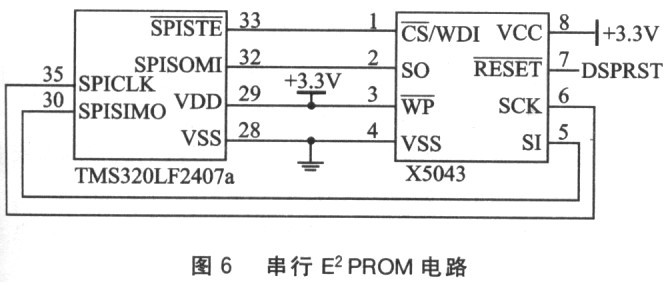

由于被烧写到片内程序Flash中的程序在运行时不能被改写,而实际工作状态中又要根据需要对一些参数进行设置,因此,为控制系统扩展了一块型号为X5043PI-2.7,存储容量为4K的串行E2PROM,与DSP的串行外设接口模块(SPI)连接实现参数设置、存储功能,如图6所示。

SPICLK为SPI单元的时钟信号输出引脚,为X5043PI-2.7提供时钟信号。SPISIMO为从动输入、主动输出引脚,与X5043 PI-2.7的从动输入引脚相连;SPISOMI为从动输出、主动输入引脚,与X5043 PI-2.7的从动输出引脚相连。SPISTE作为一般I/O口使用,为X5043PI-2.7提供片选信号。

2 外围硬件电路设计

2.1 信号调理与A/D转换

电力系统中的电压电流信号一般不能直接送到A/D器件的输入端供转换,而要先经PT、CT将电压电流降低,再经过互感器、信号调理等预处理后供A/D转换。图中反馈电阻R2和R3用来调节输出信号的大小。电容C2及可调电阻R1用来补偿互感器的固有相移。电容Cl和C5是400~l000pF的小电容,用来去耦和滤波。两个反接的二极管用来保护运算放大器。运算放大器视精度要求而定,常用精度和稳定性良好的OP07。运算放大器电源电压通常取±15V或±12V。运放LT084接成射极跟随的形式,起到阻抗匹配的作用。

A/D转换是控制系统中的必备重要环节,其转换精度决定了整个控制系统性能的优劣。虽然2407aDSP内置10位高速A/D模块,但该模块存在以下缺点;只能接收0~3.3V的单极性信号输入,对于交流信号需要另外设计限幅抬压电路;同一排序器内各通道串扰严重;10位的转换精度难以满足高性能系统的要求。本文选用Maxim公司的14位高速A/D芯片MAXl25作为外部模数转换器。其输入信号范围±5 V,通道最大承受过压可达±17V,简化了信号调理电路;单路转换时间3μs;拥有A、B两组信号输入端,每组四个输入通道,内置四路采样保持器。MAXl25可以和DSP并行工作,从而减轻了DSP的工作负担。MAXl25数据、地址线通过总线隔离驱动芯片74HC245与2407aDSP的数据线连接,片选信号由GAL提供,电路结构如图4所示。

2.2 键盘与液晶显示

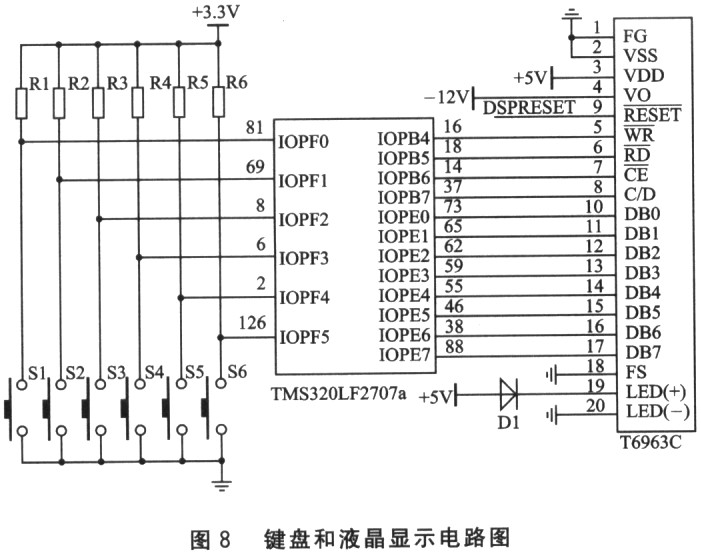

2407a DSP有多达41个通用、双向的数字I/O引脚,其中大多数都是基本功能和一般I/O功能复用。将IOPF0~IOPF5六个端口设置为一般I/O口输入方式,实现键盘输入功能。液晶显示器采用内藏T6963C控制驱动器图形液晶显示模块。T6963C是大规模点阵式图形液晶显示控制器,通过8位并行数据总线和一组控制总线进行指令和数据传递。采用间接控制方式实现对液晶显示模块的控制,即DSP的IOPE0~IOPE7与T6963C的数据线相连,IOPB4~IOPB7分别与T6963C的写选通信号、读选通信号、片选信号和通道选择信号相连,实现控制功能。与直接访问方式相比,间接方式减轻了总线负担。键盘与液晶显示电路结构如图8所示。

2.3 同步电路设计

装置中,功率器件的控制信号都必须以某时间基准为参考,因此同步信号相位的准确性直接影响电力电子装置的性能。通常同步信号取至系统电源电压。图9为同步信号采集电路,一次侧电压经PT降压后,经通带中心频率为50Hz的硬件带通滤波器滤波后,比较器LM311将交流正弦信号转换为同频同相方波信号,再通过与门整形后用光耦4N25实现隔离与电平转换,输出信号送入DSP的捕获引脚,供捕获单元上跳沿中断。通过合理配置Rl、Cl、R2、C2的参数,可实现对50Hz的有效信号不相移的滤波环节,从而避免了采集电路带来的附加相移。

3 制作PCB板注意事项

①控制器的PCB板最好制成四层板(即除了顶层和底层外,添加了电源层和地层,用内层分割技术可以把3.3V和5V放在一层,模拟地和数字地放在一层),可明显提高整个系统的抗干扰性能。一般情况下,四层板比两层板的噪声低20 dB。四层板效果虽好,但制作费用高,且不易查错。双面板最好在顶层和底层都铺铜,分别与系统数字地线和电源线连接,也可起到很好的抗干扰效果。

②铜膜线宽的最小值取决于流过它的电流大小,一般不宜小于O.2 mm。只要电路板面积无特殊限制,线宽和间距最好选用0.3mm。通常情况下,l~1.5mm的线宽允许流过2 A的电流。地线和电源线宽度最好不小于l mm。

③Protel 99 SE没有提供2407a的封装,需要依据原文资料提供的尺寸自行创建。用Prote1 99 SE的向导自动生成封装既方便,精度又高.因为2407a为贴片式封装,引脚细小,间距窄。建议把引脚设为长1.50mm,宽0.35mm,引脚间距0.50mm.这样容易焊接,不易造成短路。

④所有连接DSP时钟模块的导线必须尽可能短。当连接PLL引脚时,应注意以下几个方面:使用短引线连接PLLVCCA引脚到低通滤波器;使旁路电容最近连接到PLLVCCA和VSS间;使这些导线、芯片和旁路电容形成的环路面积最小。面积越大则电磁干扰越大。

⑤PCB板上的数字地与模拟地应分开布线,通过电感或磁珠单点连接,避免互相干扰。因为一般数字电路的抗干扰能力强,TTL电路的噪声容限为0.4~0.6V,CMOS数字电路的噪声容限为电源电压的O.3~0.45倍;而模拟电路部分只要有微伏级的噪声,就足以使其工作不能正常。

⑥在DSP和其他芯片的电源与地之间就近跨接0.Ol~0.1μF的去耦电容,以提供和吸收芯片通断电瞬间的充放电电能,且能旁路芯片产生的高频噪声。

基于TMS320LF2407aDSP的电力电子装置控制器,具有通用性。通过在有源电力滤波器装置中使用,证明该控制系统各单元工作可靠,整体配合良好。对从事相关硬件设计的工程技术人员,有一定的参考价值。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)