CPLD在多功能谐波分析仪设计中的应用

1采样方法比较

对三相电压、电流6路模拟量进行数据采集时,一般有两种方法:①同相电压电流交替采样法:在被测信号的一个周期内,采样256点,其中128个奇数点为电压采样点;128个偶数点为电流采样点。采电压和采电流的时差为Δt=T/256(T为被测信号周期)。由Δt引起的同相电压电流的相位误差为δui=360*f*n*Δt(度)。式中f――被测信号频率,n――谐波次数。由上式可知相位误差随时差Δt、谐波次数n增大而增大,这是造成相位差存在并且不一致的根本原因。另外还有一个原因,当电网频率畸变时,由于采样是定时采样,不能跟随频率变化,也会造成测量误差。②同相电压电流整周期同步采样法:同相电压、电流采取的是同步采样,分时传输的方法。这样,就不存在时差问题,相位差也就不存在;对于电网频率畸变的问题,常用的方法是锁相环技术。它是通过对电网电压信号取样进行带通滤波,提取出电网基波信号,然后进行整形处理,获得与基波信号频率一致的方波信号,将它进行锁相倍频,获得输出频率为f0=N*fi的方波信号,以此作为整周期同步采样脉冲信号。由此,采样间隔也就随被测信号的频率变化而相应变化,但是,这又增加了硬件的开销。在本设计中,采用的是整周期同步采样方法:由CPLD和单片机配合产生符合要求的整周期同步采样脉冲信号。

2工作原理及硬件构成

2.1系统的工作原理

首先让被测信号经过抗混叠低通滤波器电路进行预处理,对其中1路信号通过测频模块进行精确的频率测量,把频率参数传输到单片机,由其通过运算确定分频系数,然后,回送到CPLD的总控制器中,总控制器由此产生采样脉冲信号。在采样过程中,对于同相电压、电流信号采用的是同步保持,通过多路开关分时采样。其中,3路采样保持器的控制信号Ca,Cb,Cc,多路开关的地址选通信号A1,A2,A3由CPLD控制产生。把选通的1路信号送入AD开始转换,并检测转换结束信号。当一次AD转换结束时,通过RAM地址发生器产生的地址和读写控制时序,把AD转换的结果直接送入双口RAM存储。然后,进行下一次采样。当A相信号采样完成后,就顺序采样B相、C相信号。本设计中的MCS?51单片机主要负责运算及人机接口的管理,这将大大提高整个系统的运行效率,提高了运算的精度,又兼顾了运算的响应速度。

2.2主要硬件的选择

由于CPLD是高速器件,所以在采样频率很高的时候,多路开关和AD转换器就成为制约采样频率的主要因素。当采样频率达到兆级的时候,RAM的存储速度又成为了另外一个制约因素。

在本设计中,要求分析的谐波次数达到50次,被测信号在45Hz~55Hz范围内,频率自动跟随。根据香农定理知:采样频率应该大于或者等于被测信号频率的2倍。要求每个周期采样128点,这样总的采样频率为f=128*55*2=14.08kHz,所以采样周期为T=1/fs=71.02μs。采样保持器选择AD582,它是反馈型结构,在精度要求不高(≤0.1%)而速度要求较高时,可选用CH=1000pF,捕捉时间tAC≤6μs。多路开关选用MAX382,它开关速度快,在双电源,连续供电工作方式下,典型开关时间在100ns左右。它的主要特点是:工作电压低、通道电阻小(≤100Ω)、具有数字输入锁存、TTL/CMOS电平兼容、具有ESD静电保护功能等。ADC转换器选用MAX172,该芯片是5V电源供电的12位模数转换芯片,CMOS工艺制造,速度快,转换时间为10μs,具有基准源,外接时钟,频率要求为1.25MHz。

2.3CPLD器件简介

3CPLD内部电路实现

本设计的软件是在MAX+plusII10.2下完成的,顶层文件是*.gdf图形文件,低层用AHDL硬件描述语言来描述。

3.1测频模块

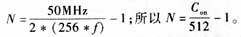

测频模块的主要作用是:①测量电网频率;②确定分频系数,产生跟随频率变化的同步脉冲。测频原理:由于测量的频率在50Hz左右,采用脉宽测量方式,即首先对被测信号进行2分频,使信号的正负脉宽相等,然后利用正脉宽对50MHz的标准脉冲进行计数。正脉宽上升沿来时,计数器开始对标准脉冲计数;下降沿来时,锁存当前的计数值Con。通过以下关系确定频率f、分频系数N。

分频系数为:系统时钟源频率与分频得到脉冲频率(256*f)的比值的一半再减去1,即

3.2S/H时序控制模块

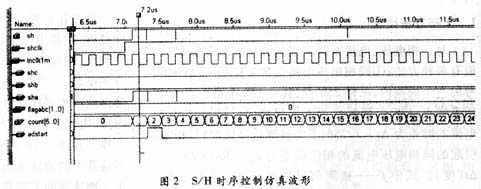

由于采用的是同相电压、电流同步采样技术,所以对S/H的控制时序要求严格。同步采集某相电压电流1次的时间≤71.02μs。同相电压、电流间要求是同时保持,分时采样。由于ADC582的捕捉时间约为6μs,所以S/H时序脉冲低电平应至少为10μs,在此期间,采样保持器处于跟踪状态;高电平为60μs,在高电平期间,采样保持器处于保持状态。前30μs对电压信号进行AD转换并存储;后30μs对电流信号进行AD转换并存储。仿真波形如图2。

3.3多路开关MAX382的地址产生及ADC控制模块

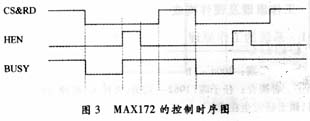

在AD582控制脉冲一个周期的高电平期间,要采集电压、电流各1次,所以多路开关MAX382需要选通2次,AD芯片MAX172也需要启动2次。第1次MAX382选通起始于AD582控制脉冲上升沿来临以后的1μs时刻;第2次起始于中间31μs处,延时1μs。这是因为采样保持器的输出还有一段波动,经过一定时间tST才保持稳定,为了量化的准确,所以在保持指令发出后,延时1μs。AD启动脉冲开始于AD582控制脉冲2μs、32μs处,也延时1μs。MAX172的控制端有:CS,HEN,RD;转换结束状态线:BUSY。当CS=0,RD=0,BUSY=0时,AD正在转换;BUSY=1时,转换结束;HEN=1,读转换结果的高4位数据,HEN=0时,读转换结果的低8位数据。该模块要结合硬件来仿真。MAX172的控制时序图如图3。

?

3.4双口RAM地址发生器及读写控制模块

ACEX1K100器件内嵌EAB单元,可构成容量大约??KB的双口RAM,由于MAX172?位AD,而MCS-51的数据总线只??位,所以,需要??次采样的数据分??个字节,分别存储。因为电压、电流分时交替转换,所以,在地址发生器中要有一个确定的映射规则,调整其存储地址,以使电压、电流在双口RAM中分块顺序存储。另外,在双口RAM中,当对同一地址单元同时进行读写时,要有一个仲裁机制,对其进行控制;当读写发生冲突时,我们约定:CPLD写双口RAM具有优先权,只有当写 *** 作结束后,MCS-51单片机才被允许读该单元。该模块的仿真波形见??。

3.5通信模块

该模块是在CPLD内部构建一个串行发送电路端口,实现MCS-51单片机与CPLD器件之间的通信功能。(1)在正常工作模式下,频率、同步脉冲的分频系数等重要数据需要通信。(2)在系统升级模式下,单片机发送控制数据给CPLD实现升级。通信方式为串行单工通信,MCS-51单片机发送数据,CPLD接受数据。通信波特率约定?bps,通信的帧结构???位数据??位起始位(低电平)??位数据位,低位在前??位停止位(高电平)。帧与帧之间??位空闲位(高电平)以确保通信正确。?

?

4结论

在电力谐波分析仪的设计中,CPLD的应用使采样的速率大大提高,由于采用频率跟随技术,可以满足高精度的测量需要。另外,也减轻了MCS-51单片机的负担,提高了系统的响应速度,实时性更强。该设计还有另外一个优点,系统升级方便,只要把ADC芯片换成MAX162,单片机的程序稍做修改即可。当然也可以实现在线修改,实现远程控制等功能。

参考文献

[1]仇润鹤,任子晖,等.单片机在电网谐波分析仪中的应用[J].中国矿业大学学报,1994,23(1).

[2]徐会明,卢锦凤,等.GXY-90工频谐波分析仪设计中的几项先进技术[J].仪器仪表学报,1994,15(2).

[3]李绍铭,杨伟翰,等.高速数据采集与谐波分析仪的设计[J].自动化仪表,1999,(12).

[4]付慧生,袁小平,庄乾起.复杂可编程逻辑器件与应用设计[M].中国矿业大学出版社,2003.

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)