首先分析了8PSK 软解调算法的复杂度以及MAX算法的基本原理,并在Altera 公司的StraTIx II 系列FPGA芯片上实现了此软解调硬件模块,同时与LDPC 译码模块进行了联合验证。通过软硬件验证和分析表明,此设计在运算复杂度、吞吐量、最终误码性能上取得很好的折中。

1 8PSK 软解调原理

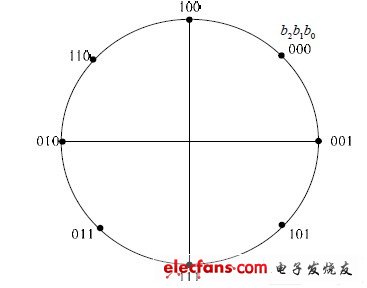

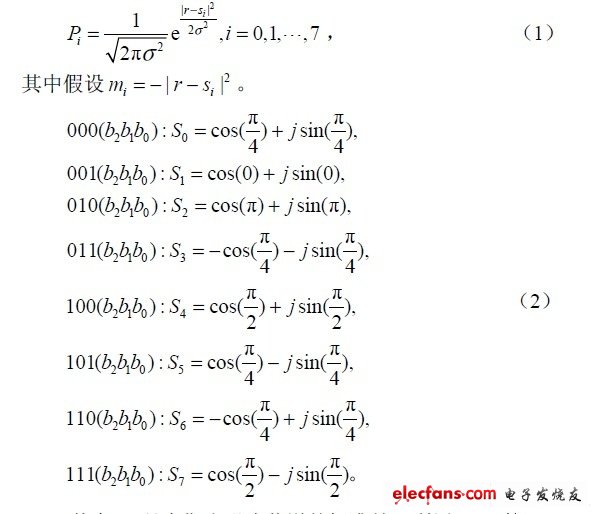

8PSK 的调制星座图如图1 所示,每个符号代表三个比特, 式(1)表示经过高斯白噪声信道后接收信号的概率密度函数,式(2)描述了星座图上每个星座点的值,Si 代表该星座图上1 到8 个星座点。

图1 8PSK 调制星座

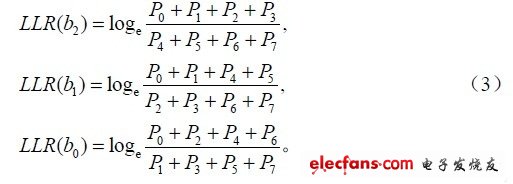

其中σ 是高斯白噪声信道的标准差。利用LLR 算法,软判决如式(3)所示,其中分子上的各项表示此比特为0的概率之和,分母各项表示此比特为1 的概率之和。

从式(2)和式(3)可以看出,每计算一比特的LLR,都需要平方、指数和对数运算,因此LLR 算法具有较高的运算复杂度和较大的资源开销,尤其是硬件实现指数、对数复杂度高,所以LLR 算法不适合FPGA 实现。而最大值(MAX)算法能有效避免计算每比特对数似然值的指数和对数运算,其原理如式(4)所示。

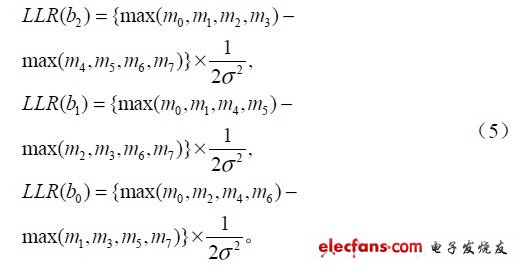

由式(3)和式(4)可知,简化以后的MAX 算法如下式(5)所示,对于式(3)和式(5)可知,LLR 算法在硬件上很难实现指数和对数运算,而MAX 算法只需要简单的加减运算和少数乘法运算,易于工程硬件实现,因此选取MAX 算法作为硬件实现的最终方案。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)