引 言

数字信号发生器是在电子电路设计、自动控制系统和仪表测量校正调试中应用很多的一种信号发生装置和信号源。而正弦信号是一种频率成分最为单一的常见信号源,任何复杂信号(例如声音信号)都可以通过傅里叶变换分解为许多频率不同、幅度不等的正弦信号的叠加,广泛地应用在电子技术试验、自动控制系统和通信、仪器仪表、控制等领域的信号处理系统中及其他机械、电声、水声及生物等科研领域。

目前,常用的信号发生器绝大部分由模拟电路或数字电路构成,体积和功耗都很大,价格也比较贵。随着微电子技术和计算机技术的发展,以DSP微处理器及DSP软硬件开发系统(例如集成开发环境CCS)及配套产品为内容已形成了庞大并极具前途的高新技术产业,而可编程逻辑器件、SOPC等新技术的应用迅速渗透到电子、信息、通信等领域。这里分别借助DSP芯片运算速度高,功耗低,实时分析的优势以及SOPC技术灵活的可配置性、较高的可靠性、硬件升级容易等优点设计了正弦信号发生器,并对各自设计过程及优缺点进行了对比。

1 基于DSP设计正弦信号发生器

1.1 正弦波产生原理

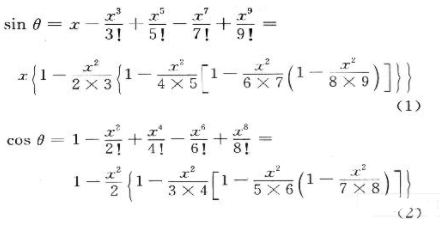

一般情况,产生正弦波的方法有两种:查表法和泰勒级数展开法。查表法是使用比较普遍的方法,优点是处理速度快,调频调相容易,精度高,但需要的存储器容量很大。泰勒级数展开法需要的存储单元少,具有稳定性好,算法简单,易于编程等优点,而且展开的级数越多,失真度就越小。本文采用了泰勒级数展开法。一个角度为θ的正弦和余弦函数,可以展开成泰勒级数,取其前5项进行近似得:

式中:x为θ的弧度值,x=2πf/fs(fs是采样频率;f是所要发生的信号频率)。

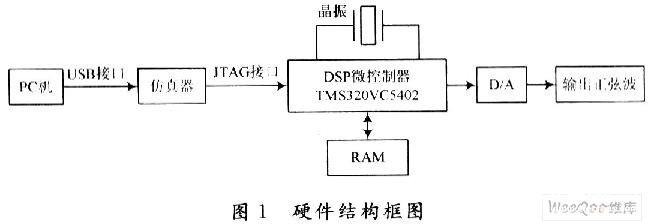

1.2 硬件设计

系统硬件主要由微机、DSP芯片、数/模转换模块组成。其中,DSP芯片采用的是TI公司性价比良好的TMS320VC5402。它有一组程序总线和三组数据总线、高度并行性的算术逻辑单元ALU、专用硬件逻辑片内存储器、增强型HPI口和高达100 MHz的CPU频率。它可以在一个周期里完成两个读和一个写 *** 作,并且具有专门的硬件乘法器,广泛采用流水线 *** 作,提供特殊的DSP指令,可以用来快速地实现各种数字信号处理算法。D/A采用了一种双极型8位、低功耗数/模转换器DAC08,实现了高速同步数/模转换。硬件结构框图如图1所示。

1.3 软件设计

软件设计是基于CCS开发环境的。CCS是TI公司推出的为开发TMS320系列DSP软件的集成开发环境,是目前使用最为广泛的DSP开发软件之一。它提供了环境配置、源文件编译、编译连接、程序调试、跟踪分析等环节,并把软、硬件开发工具集成在一起,使程序的编写、汇编、程序的软硬件仿真和调试等开发工作在统一的环境中进行,从而加速软件开发进程。本文采用了与硬件开发板相结合的在线编程模式,通过CCS软件平台上应用C语言及C54X汇编语言来实现正弦信号发生装置。

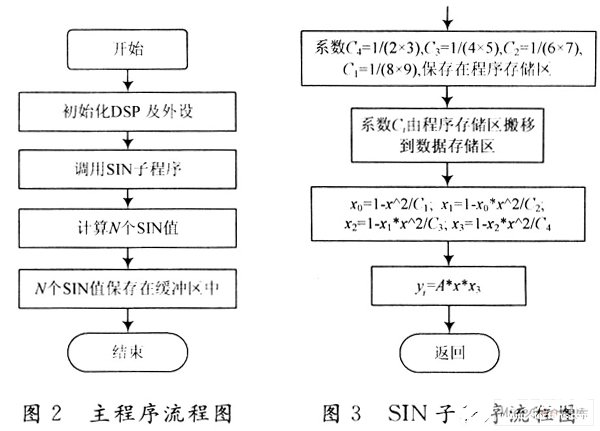

软件设计的思想是:正弦波的波形可以看作由无数点组成,这些点与x轴的每一个角度值相对应,可以利用DSP处理器处理大量重复计算的优势来计算x轴每一点对应的y的值(在x轴取N个点进行逼近)。整个系统软件由主程序和基于泰勒展开法的SIN子程序组成,相应的软件流程图如图2和图3所示。

程序中,N值为产生正弦信号一个周期的点数,产生的正弦信号频率与N数值大小及D/A转换频率fDA有关,产生正弦波信号频率f的计算公式为:

f=fDA/N

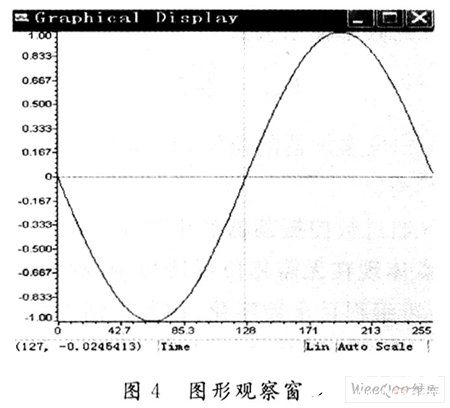

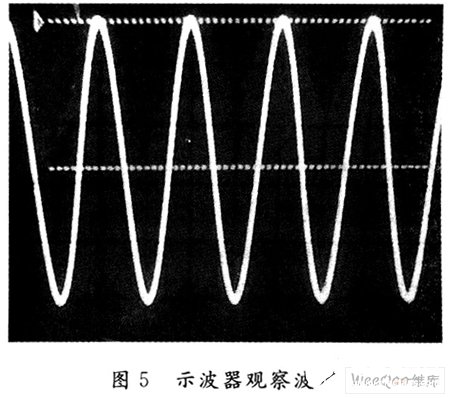

因此,选择每个正弦周期中的样点数,改变每个采样点之间的延迟,即通过调节N值产生不同频率的波形,同时也可以利用软件改变输出的离散波形值乘以相应的缩放因子A,从而调节波形的幅度。将程序装载到DSP目标芯片中,波形实现结果可以在CCS图形显示界面直观地表示出来(见图4)或者用示波器观察输出结果如图5所示。

输出结果显示,在CCS图形观察窗口得到了频率稳定,信号干扰小,波形失真度较小的正弦信号;利用示波器也可观察到波形较好,稳定的正弦信号。

2 基于SOPC技术设计正弦信号发生器

尽管DSP处理器(如TI的TMS320系列)在过去很长一段时间几乎是DSP应用系统核心器件的惟一选择。但由于其自身的局限性,例如不灵活的硬件结构,使得其很难满足当今迅速发展的DSP应用市场。现代大容量、高速度、内嵌有各种DSP模块的FPGA和相应的SOPC技术出现,使得数字信号处理的实现更加容易。

2.1 DDFS原理

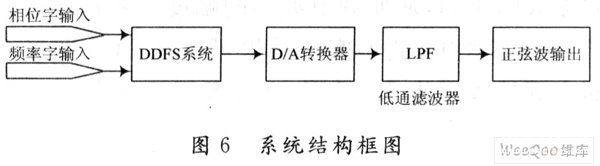

直接数字频率合成(DDFS)电路由系统时钟、相位累加器、频率累加器、波形查找表、D/A转换器和信号调理电路构成。DDFS的工作原理是在每个时钟周期,用频率累加器以输入频率字FW为步进进行自增累加,累加结果的高位送相位累加器,并与输入的相位字PW进行累加,相位累加的输出作为波形查找表的地址,从查找表中读出相应的数据送给D/A转换器,最后经过低通滤波器、后级放大等信号调理电路,以形成模拟量波形输出。图6给出系统结构框图。

DDFS的频率输出公式:

式中:N为相位累加器的位宽;M为频率字位宽;Fclk为系统时钟信号。

DDFS通过数控振荡器产生频率、相位可控的正弦波。其优点体现在无需相位反馈控制,频率建立及频率切换较快,可编程且全数字化,控制灵活方便,输出相位连续。如果在相位累加器的位数N足够大时,理论上可以获得很高的分辨精度,应用DDFS还可以产生其他多种调制信号,因此具有极高的性价比。

2.2 硬件模块设计与仿真

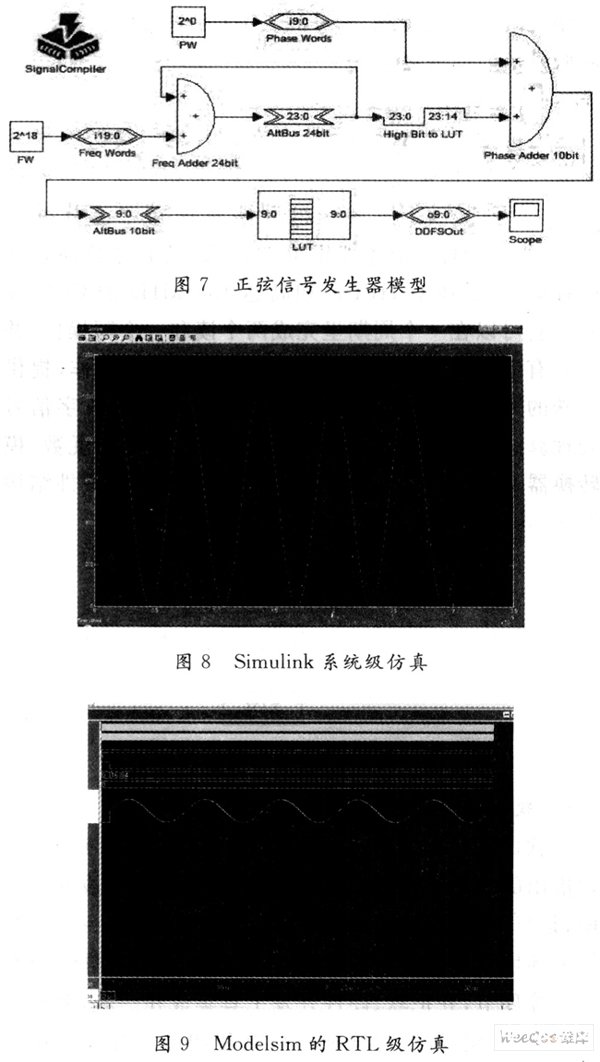

利用DSP BuiIder进行DSP模块设计是SOPC技术的一个组成部分。关键设计过程在Matlab的图形仿真环境Simulink中进行,用图形方式调用DSP Builder和其他Simulink库中,图形模块,构成系统级设计模块,如图7所示。

模块化设计的主要优点在于只要改变模块中的状态字就可以轻松地控制正弦波的频率和相位,不用到程序里修改了,也不需要理解复杂难于掌握的硬件描述语言,真正做到模块化并充分节省设计时间和设计周期。

电路模型设计完成后,可以利用Simulink环境的强大的图形化仿真验证功能,直接进行算法级模型仿真验证,结果如图8所示。由于在Matlab的Simulink中,模型仿真属于系统验证性质的仿真,并不是RTL级仿真,与目标器件和硬件系统没有关系。因此采用Modelsim对设计电路进行功能仿真。Modelsim是Mentor公司杰出的HDL仿真工具,以其强大的数字和模拟仿真功能而广泛应用,且仿真结果直观、易懂,如图9所示。

由图8和图9输出波形结果可以看出,采用SOPC方案设计的正弦信号发生器产生的正弦波波形清晰、稳定、相位变化比较连续,且输出相位噪声低。

2.3 系统硬件验证

通过SignaICompiler把设计模型文件转成相应的硬件描述语言VHDL设计文件。在QuartusⅡ集成环境中,对.vhd文件进行编译、时序仿真,对设计文件进行仿真验证,确定DE2开发板中PIO所对应的输入/输出即引脚锁定;对器件编程并最终下载到目标芯片DE2EP2C35F672C6上,以实现硬件测试;调用Signal-TapⅡ观察硬件测试结果,经D/A转换由示波器观察波形输出,其结果与系统仿真结果相同,从而验证了系统设计的合理性。

3 结 语

从工程应用的角度,提出了基于DSP及SOPC的结构化、模块化设计方法,该方法可以推广到其他电子设计领域,使系统电路设计更加简便直观,且便于扩展,具有较高的实用性和可靠性。通过对比DSP和SOPC设计的优缺点表明,与DSP设计相比,SOPC技术可以大大缩短系统的设计周期,节省设计费用,提高产品的性价比和竞争力,因此更具有良好的推广和应用前景。

责任编辑:gt

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)