高速压电致动器的生产成本在过去15年以来越来越价廉,因此越来越多的应用设计倾向于采用高速压电致动器。压电致动器最初用于医疗设备,包括上世纪80年代末的手术工具和超声波检查。这在那时是很有道理的,因为压电致动器具有微秒级的响应时间,是响应速度最快的定位元件。此外,它们还能够产生以亚纳米量级为步长的运动。因此,采用这种器件进行产品设计的公司的数量急剧增加也就不足为奇了。

压电致动器要求高压驱动器能提供峰峰值为数百伏特的电压。此外,由于典型的致动器实质上看起来像一个驱动放大器的纯电容,所以几乎所有的功率消耗都为驱动放大器带来负担。

纵观大量的高速、小信号运算放大器,可看出许多放大器都具有数百兆赫的带宽。但若设计目的是驱动高速压电器件,就必须同时兼顾速度和12V以上的电压,这时放大器的可选择范围就急剧缩小。此外,选择基于MOSFET单片放大器的设计还有许多有吸引力的优势。

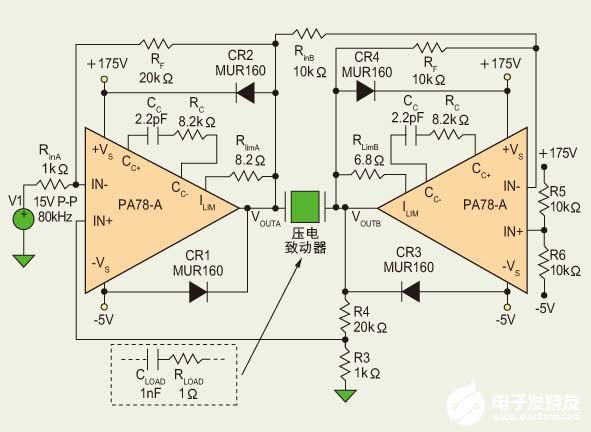

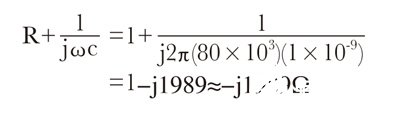

这里的压电致动器电路在80kHz频率下需要一个电压峰峰值为300V的电源,以驱动致动器。可以通过一个串联了1Ω电阻的1nF电容来表示这个致动器(图1)。

图1:在这个桥式电路配置中,两个PA78驱动压电致动器,PA78由-175V和-5V不对称电源供电。

选案评估

在决定哪种方案最适合驱动压电致动器之前,我们需要根据应用情况,对几种可选方案进行评估。

单个放大器的方案:该方案的问题主要在于成本。压电致动器要求电压范围为+150V到-150V,而市场上唯一满足该要求的80kHz器件是混合型的,单价在100美元以上。

电平移动式小信号放大器:如果一个设计从小信号放大器开始,接下来再设计电平移动,这将意味着需要采用大量分立式元件从头开始构建设计。在这种情况下,非重复性工程的工作量非常大,设计时间很长且成本很高。

高压、高速、低电流MOSFET运算放大器IC:本设计选用的单片集成电路PA78利用A/B类驱动器级来驱动输出MOSFET,利用新型输入级来获得非常高的压摆率(slew rate),同时还消除了传统运算放大器设计的高静态电流。该设计需要采用两个PA78。这种放大器单价大约为15美元,与混合型器件的100多美元相比,其费用得以大大降低。

图1的桥式电路配置了两个PA78。在这种配置中,放大器提供的输出电压摆幅是单个运算放大器的两倍,压摆率也增加了一倍。任何非线性都变成对称的,和单个放大器的电路相比,这能减少二次谐波失真。

由正弦信号源在80kHz下提供15V峰峰值信号来驱动放大器对,放大器对再驱动压电致动器。本例假设压电致动器的阻抗等于1Ω电阻和1nF电容的等效串联阻抗。

在这个应用中,负载是浮空的,即负载完全没有接地。当左边的输出VOUTA从10V上升到160V(图2a),右边输出VOUTB从160V降至10V(图2b)时,负载上的电压摆幅为300V(-150V到+150V)(图2c)。

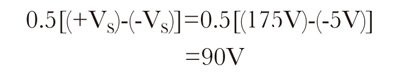

两个放大器的输出现在是反相的。桥式配置电路中两个PA78的总增益为+20,因此需要向压电致动器提供所需的300V峰峰值电压。由电阻R3和R4组成的反馈电路使两个PA78模块的输出都以大约85V为中心。在图1,一个双源、非对称电源为两个放大器模块提供+175V和-5V电压。

图2:当图1中左边输出VOUTA从10V上升到160V(图2a),右边输出VOUTB从160V降至10V(图2b)时,负载上的电压摆幅为300V(-150V到+150V)(图2c)。

确定+VS和-VS的净空余量

必须谨慎选择+VS和?CVS的值,以确保在VOUTA和VOUTB发生正/负偏移(posiTIve and negaTIve excursions)期间有足够的净空(headroom)。输出(VOUTA-VOUTB)的值在+150V到-150V之间摆动。但在这种非对称源结构中,放大器的共模输入范围(CMR)的正负值在控制+VS和?CVS值上起着重大作用。

在PA78的例子中,CMR的负值规定为?CVS+3V,这意味着输入电压与负电源轨之间的差值不应小于3V。因此,通过选择?CVS等于-5V,可让VOUTA和 VOUTB(有10V的负偏移)与电源负轨之间的差值大于15V。CMR的正值为+VS?C2V,这意味着VOUTA和VOUTB的最大正偏移必须保持低于+VS至少2V。

关于+VS电源轨的第二个问题是,模块输出峰值电流时输出端的电压降问题。在这个应用中,峰值电流大约为75mA。从PA78规格手册中一个称为“输出电压摆幅”的图可知,如果输出这个峰值电流,电压将下降8V。2V和8V加起来就是10V,即+VS必须超过150V的最大电压摆幅至少10V。选择175V的+VS就意味着具有15V的额外净空余量。

对任何压电致动器电路而言,防止信号误馈回到放大器至关重要。压电传感器能很容易地将机械能转换为电能和将电能转换机械能,因此传感器如果受到撞击,将产生大量回流到放大器输出的能量。当然,这种能量的破坏性很大。不过,只要简单地在每个放大器的输出端到其对应的电源轨之间连接几个超高速二极管MUR160(CR1至CR4),就可以为每个放大器提供保护。

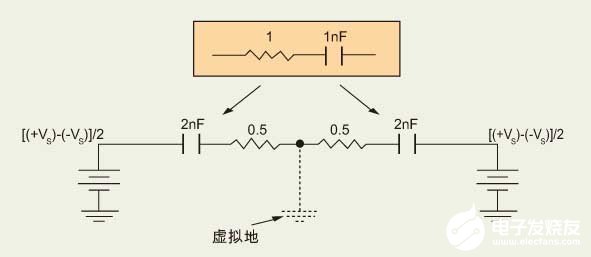

图3:计算最大功耗的等效电路图。

功耗计算与散热处理

压电式拾音头的负载阻抗由下式给出:

上式假定R=1Ω,C=1nF,ω=80kHz。

为计算每个模块的最大功率,需要用到图3给出的等效电路。首先,将图1电路分为两部分,每一部分都包含一个2nF电容和一个0.5Ω电阻,并假设虚线和符号代表接地。因为阻抗的实部(1Ω)与1989Ω的总容抗相比很小,可忽略不计。

在这个等效电路中,施加的电压将等于施加在每个模块上的总电压的一半。

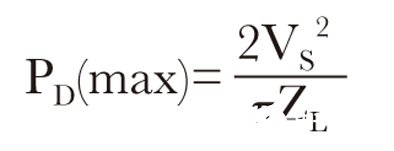

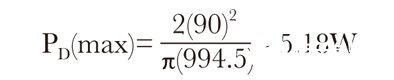

每一半的电路输出驱动一半的容抗负载,即994.5Ω。为确定功耗,首先要知道负载上电压V和电流I之间的相位差。由于本例把负载作为一个纯电容来建模,所以相位角φ等于90°。当存在电抗性负载,相位角大于40°时,可由下式计算最大功耗:

这里,VS是每个电源的电压幅值,ZL等于负载阻抗。

因为负载是完全电抗性的,所以负载不消耗功耗,每个PA78放大器IC的功耗为5.18W。然后选择散热器,并确认每个PA78的温度不超过的最大允许结温。

HS27散热器是为安装PA78 IC而选择的。每个散热器的热阻为5.3℃/W,正如我们已确定的,每个放大器的功耗为5.18W。

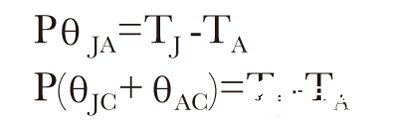

必须确认PA78内MOSFET器件的结温不会超过安全值。常用的热阻计算公式如下:

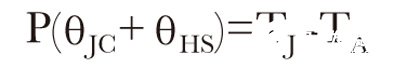

可以用散热器的热阻θHS代替θCA,上式变为:

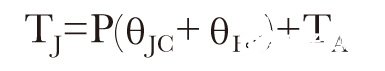

我们需要利用上式求出TJ,以确认不会超过最大结温。式(6)通过移项变为:

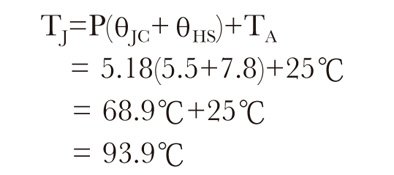

在这个例子中,根据PA78规格手册,每个器件的功率是是5.18W,θJC为 5.5℃/W。散热器的θHS为7.8℃/W,温度比周围环境高48.2℃。(散热器热阻是功率的函数,且接口界面的温度升高)。

于是,可求得最大结温为:

因此,实际的TJ不会高于93.9℃,远低于PA78规格手册规定的最大值150℃。当为高电抗性负载(比如压电致动器)提供高功率时,很有必要检查耗散区和安全工作区。

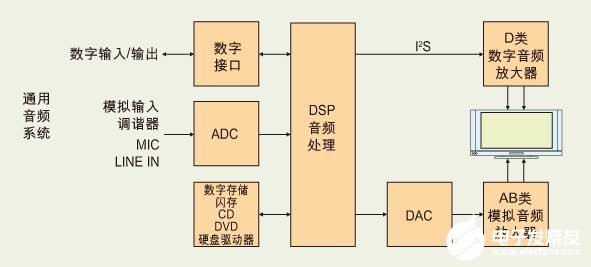

过去,工业级的功率放大器不得不牺牲带宽来保证单位增益的稳定性。双极型的设计并非总能满足要求严格的应用(比如本文讨论的压电致动器设计)的线性要求,但在器件采用基于MOSFET的架构,可以改善这种状况。

责任编辑:gt

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)