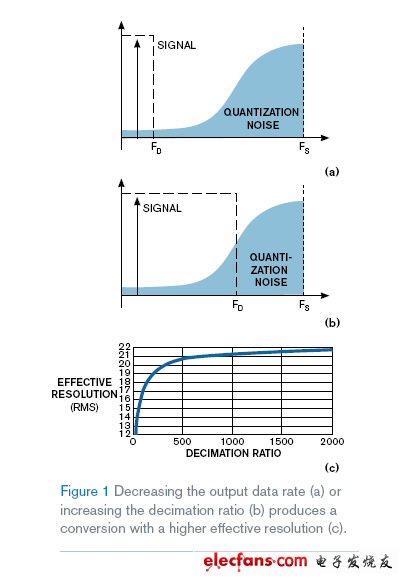

本文是对 Δ-Σ ADC 内部工作原理进行简要概述的最后一部分。不管使用何种转换器,实际精度都与 ADC 传输的位数相等。当涉及信号噪声时,“有效精度”就是对模数转换有用位的描述。有效精度等于 ADC 的有效位数。调制器 FS(采样速率)和 FD(输出数据速率)的比决定了抽取或过采样,比率,其会直接影响有效精度。抽取比的范围介于 4~32,768 之间,其与每个数据输出调制器采样的数目相等。

请看下面图 1 中的频谱。假设输出数据速率为调制器采样频率的一小部分(请参见图 1a),0~FD 的输入频率均在输出信号频带中。由于噪声水平较低,因此有效精度较高。FD 的更高频率不但增加了转换器的输出数据速率,而且还降低了有效精度。虽然调制器的大部分噪声都出现在更高频率中,但是您获得的有效精度仍然较低(请参见图 1b)。图 1c 就显示了一个关于抽取比与采样 ADC 有效精度之间关系的例子。

在不改变有效精度的条件下,提高输出数据速率的一种方法就是提高调制器的采样速率。您可以通过提高 Δ-Σ ADC 的主时钟速率来提高这一速率。使用恒定抽取比后,采样速率和功耗同时升高。此外,大多数转换器都拥有采样速率的实际极限,超过这一极限后其将无法正常地工作。抽取比和有效精度之间存在着紧密的联系。保持采样速率恒定不变并保持较低的数据速率,能够让您获得较高的转换器输出有效精度。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)