引 言

高精度的时间测量在高能粒子物理研究、深空通讯、激光测距和物质成分检测等领域均有着广泛的应用。而时间测量仪器快速、高精度、高灵敏度的特点决定其必须具有高时间分辨率和高灵敏度的数据采集及处理设备,目前最常用的有数字信号中和器(Digital Signal Averager)和高精度的时间数字转换器(TIme-to-digital converter,TDC)。其中TDC的原理是通过记录一段时间内离子脉冲信号相对于触发信号(start)的到达时间和数量,继而判定粒子的种类及其含量。

但是TDC的原理决定了其固有的缺陷-“测量死区”,即当有多个粒子同时到达时,前端仪器(如飞行时间质谱仪)产生脉冲的幅度是与粒子的数量成正比的,但是TDC的原理决定了其只认为此时到达了一个粒子,从而丢失了幅度信息。故利用TDC进行定量分析时,就存在了“测量死区”。而利用超高速数字信号中和器进行测量时,由于可以同时采集到脉冲的幅度和时间信息,故可以进行高速、高时间分辨率的定量分析。

本文主要介绍了一种高精度数字信号中和器的设计与实现方法,其最小时间分辨率为333ps,测量时间范围为0~20μs,系统死时间《50ns,并已在飞行时间质谱仪器中得到应用。

1 总体结构与基本工作原理

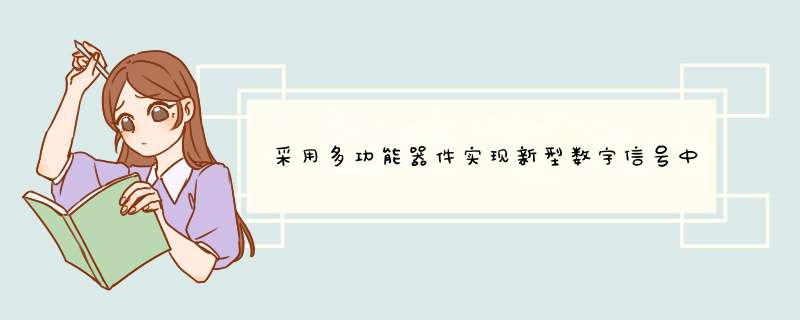

图1所示为本系统整体硬件框图,数字信号中和器主要由前端信号调理模块、射频采集模块、高速时钟产生模块、FPGA模块、USB接口模块等部分组成。其中信号调理模块主要由前置放大器ERA_1+和变压器ADTL2_18组成。射频采集模块主要由ADC08D1500及相关外围电路组成。高速时钟产生模块由ADI公司的时钟产生芯片AD9517-4组成。数据处理及控制模块由XILINX VIR-TEX-4 SX35 FPGA及相关外围电路组成。USB2.0传输及控制模块由Cypress公司的CY7C68013及相关外围电路组成。

本数字信号中和器具有内、外触发两种工作模式。在内触发工作模式下,由系统自身产生触发(start)信号,并由触发通道输出电子引导脉冲信号,以引导质谱仪前端设备。而在外触发工作模式下,系统采集外触发信号的到达以作为转换的开始。

当射频采集模块工作在单边沿采样时,通道I和通道Q为独立的stop信号采集通道,最高采样率为1.5GSPS;当射频采集模块工作在双边沿采样时,通道I和通道Q只能有一个作为信号采集通道,最高采样率为3GSPS。以外触发、双边沿采样工作模式为例。触发通道采集外部触发信号以作为转换的时间起点,脉冲输入信号经前置放大、电平转换等信号调理后,进入射频采集模块。在双边沿工作模式下,高速时钟产生电路提供1.5GHz的采样时钟,从而可以使射频采集模块的最高采样率为3GSPS。ADC采样的结果分DI、DQ、DID、DQD4组8bit差分信号以DDR的形式传至FPGA,每组差分信号的速度为375MHz。FPGA启动相应逻辑,以50us为一周期,连续采集1s,每周期内持续采样时间20us。同时FPGA逻辑控制将不同周期内相同时刻的采样点对应相加,从而得到1s内累加的质谱图。最后FPGA通过USB控制逻辑将包含脉冲数量和到达时间信息的质谱图通过USB2.0接口传至PC以完成质谱图的绘制和后端信号处理。由于射频采集ADC的最高采样速率为3GSPS,即可达到333ps的时间分辨率。针对不同的应用背景,射频采集模块的时钟频率可调,调节范围为500MHz~3GHz,即时间分辨率为333ps~2ns可调。

2 系统重要模块设计与实现

2.1 前端信号调理模块

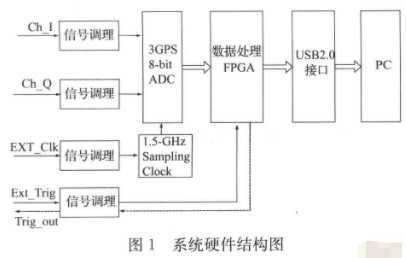

在气体行业检测的应用中,飞行时间质谱仪器中离子探测器的输出信号一般为NIM信号,幅值在0~-100mv,而超过此范围的大信号通常为H2O+及OH+等饱和信号,对测量结果影响不大,故不予考虑。由于输入信号幅度较小,为提高测量测量精度并充分利用ADC的量化范围(650mV),设计中在采集通道的信号调理模块利用微波管Mini ERA_1+完成前置放大。ERA_1+的3dB带宽为DC~8GHz,内部与50欧传输线匹配,最大增益12dB。同时,由于ADC08D1500要求差分输入,故信号调理模块在前置放大后利用射频变压器Mini ADTL2_18完成单端信号到差分信号的转换。图2所示为采集通道信号调理模块结构图。

触发通道和外时钟输入通道的信号调理模块主要由双向缓冲器及电平转换芯片组成,不再赘述。

2.2 射频采集模块

在本系统的应用背景中,输入脉冲信号的最小时间间隔为400ps,故要求射频采集模块的采样间隔小于400ps。设计中采用国家半导体公司的模数转换器ADC08D1500来构建射频采集模块,ADC08D1500为8bit双通道超高速模数转换器:在单边沿采样模式下,最高采样率为1.5GSPS;在双边沿采样(交错采样)模式下,最高采样率为3GSPS,即时间分辨率为333ps,满足设计要求。

2.3 高速时钟产生模块

为保证测量脉冲时间间隔的精度,射频采集模块需要一个高时间稳定度、最高频率为1.5GHz的转换时钟。为此,TDC选用集成锁相环芯片AD9517-4来产生时钟信号。AD9517-4是一个集成PLL频率合成器与时钟分配器,时钟稳定度《20ppm。在本系统中AD9517-4的输出频率调节范围为500MHz~1.5GHz,对应系统时间分辨率为333ps~2ns可调。

2.4 USB2.0模块

为了降低数字信号中和器对PC硬件配置的要求和数字信号中和器本身的便携性,设计中采用USB2.0接口来实现数字信号中和器与PC问的数据传输。在气体检测的应用中,飞行时间质谱仪器中的离子飞行时间较短,每秒采样的数据量较少(为几十KHz),而利用集成USB2.0控制芯片CY7C68013可实现最高为48Mbyte/s的数据传输速度,故可以满足传输速度的要求。

3 基于FPGA的数据处理

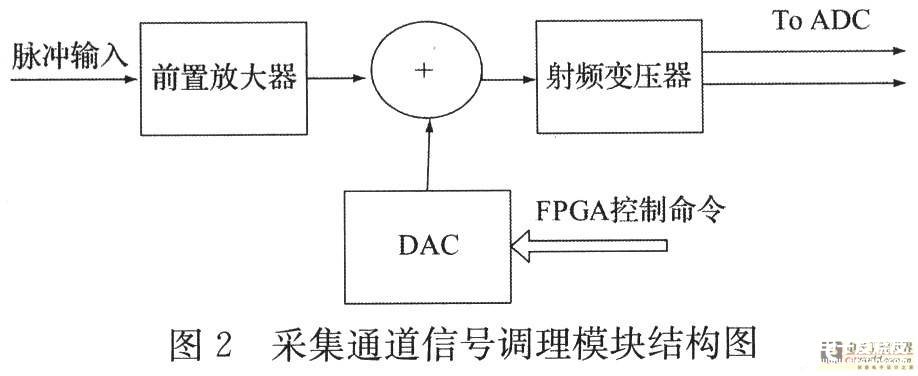

图3所示为数字信号中和器的FPGA硬件算法设计框图。设计中将硬件程序划分为AD采样缓存单元、累加器单元、存储器控制单元、USB控制单元。

3.1 A/D采样缓存单元

A/D采样缓存单元控制外部A/D芯片,并实现内部定时,每50us启动一次数据采集,每次数据采集持续时间20μs。并将采样数据存放在一深度为4的缓存中,缓存中的数据由累加器单元进行后续处理。

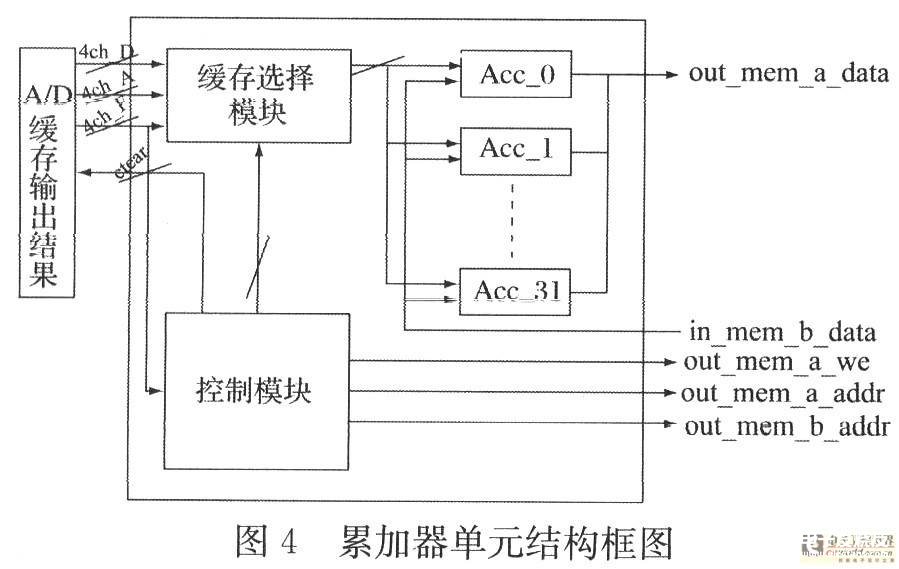

3.2 累加器单元

图4所示为累加器算法流程。当A/D采样缓存单元中的缓存有数据时,读取缓存中数据,一次读取32个采样点,将采样结果和存储器中对应地址的数据相加,并将累加再次写入存储器中的对应地址。

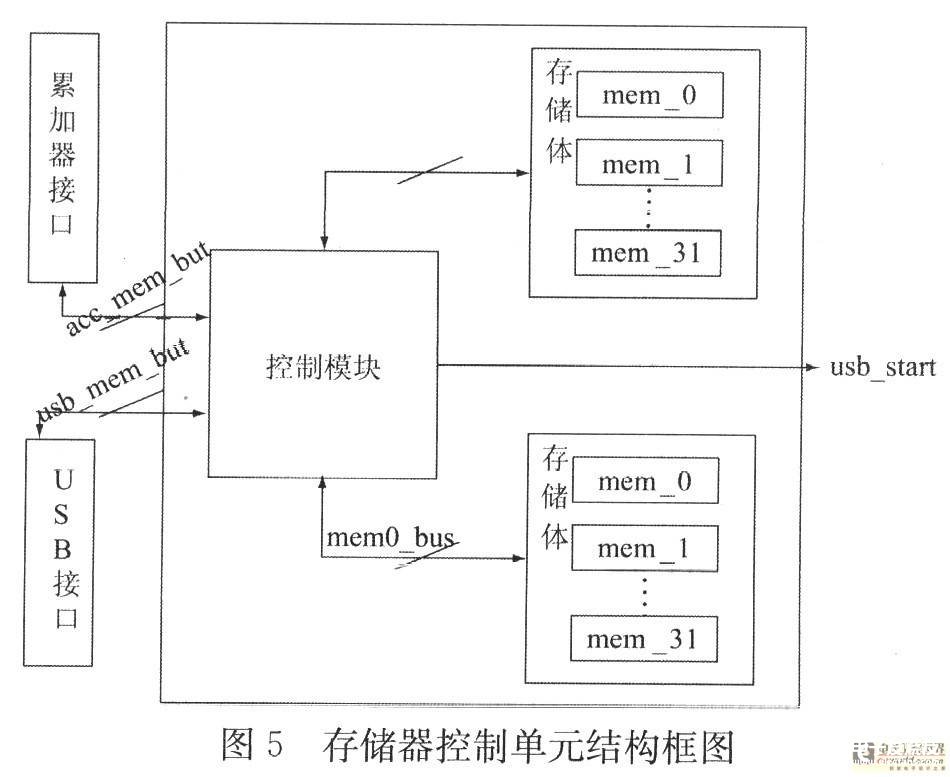

3.3 存储器控制单元

图5所示为存储器算法流程。存储器控制单元内部包含了两个存储体。任一时刻,两个存储体分别由累加器单元控制,实现数据累加;或由USB控制单元控制,将存储体中的数据传输至上位机。由存储器控制单元进行控制,两个存储器进行乒乓 *** 作,每秒进行一次切换,即每秒完成一浓累加循环。

3.4 USB控制单元

USB控制单元在每完成一秒的数据累加后,启动一次数据传输,数据传输就是由USB控制单元读取存储体中的计算结果,将结果写入USB控制器中。并在读取存储体中数据的同时,将存储体中的数据清0,为下一次数据累加做准备。

4 测试结果

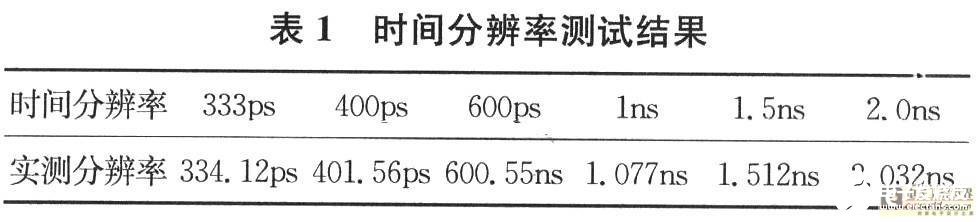

本设计中射频采集部分的采样时钟为1.5GHz,故在交错采样模式下,ADC的采样率为3GSPS。因而ADC的采样间隔为1/3GSPS=333ps,即时间间隔大于333ps的信号即可为系统所分辨,测量。实际测试中采用延迟线测量法进行时间分辨率的测试。时间分辨率测试数据如表1所示。

设计中采用FPGA内部的BlockRAM作为存储累加单元,限于BlockRAM的容量和硬件算法的设计,本系统的测量时间范围为0~20us,即在一个测量周期内只测量触发信号后20us内的信号。

5 结束语

根据飞行时间质谱仪器的应用背景,本文提出了一种基于超高速模数转换技术的高精度数字信号中和器的设计与实现方案,经实际制作与调试,本设计达到了预期的设计目标,时间测量范围为0~20us,实际测试最小时间分辨率为334ps,线性度良好。目前,该数字信号中和器已应用于飞行时问质谱仪器的相关实验中。今后的重点将针对检测动态范围、最小时间分辨率和灵敏度等主要参数进一步进行优化。

责任编辑:gt

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)