一、AT91SAM9261先进中断控制器(AIC)介绍

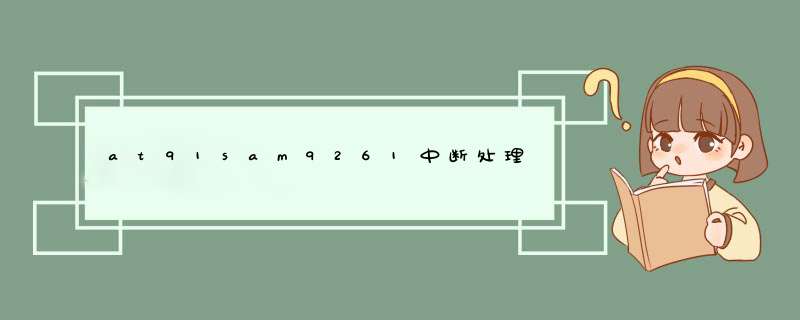

ARM核结构采用了一个简单的双中断机制,处理器内核有两个中断接口IRQ(标准中断接口)和FIQ(快速中断接口),而AT91SAM9261片内的先进中断控制器(AIC)利用这两个接口将外设的中断请求有序的传递到内核。如下图所示:

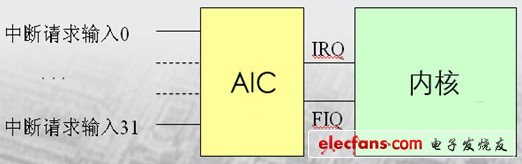

AT91SAM9261的先进中断控制器(AIC)是一个8优先级,可独立屏蔽中断的向量中断控制器,可处理32个中断源。它的设计思想是从本质上减少在处理内部和外部中断时的软件和实时系统开销。AIC驱动ARM内核的nIRQ和nFIQ,它的输入来自内部外设中断或产品引脚的外部中断。

AIC的8优先级控制器允许用户对每个中断源定义优先级。即使一个低优先级中断正在被处理,也允许高优先级的中断被服务。

内部中断源可被编程为电平有效或者边沿触发,外部中断源可被编程为上升沿或下降沿触发或者高电平或低电平有效。

快速强制特性可重定向任何内部或外部中断源为一个快速中断而不是一个普通中断。

AIC的详细方块图如下所示:

二、AIC的向量中断机制

AIC 采用“向量中断”的中断跳转机制,这种机制与三星的S3C2410芯片的中断控制器有很大不同。2410在有中断触发之后,首先会进入异常向量表,然后跳转到IRQ或FIQ服务程序,这段代码负责解析具体是哪一个中断源产生了中断,然后才跳转到具体的处理函数去执行。而向量中断的中断跳转机制则不需要软件来识别中断源,也就是不需要IRQ或FIQ服务程序,而完全由硬件自动跳转到对应的中断地址,相当于硬件帮助我们完成了一些必要的处理,减小了中断响应延时。

也就是说,AIC对于各个中断源的管理是采用硬件和软件两个方面的分发处理来完成的。首先AIC为每一个中断源向量寄存器(AIC_SVR0~ AIC_SVR31),在配置使能相应外设时用户将设备的中断处理函数地址写入对应的中断源向量寄存器,而当中断请求发生时AIC将对应的源向量寄存器中的地址复制到中断向量寄存器(AIC_IVR)并向内核发出IRQ请求,以上都是硬件实现的中断分发过程;在软件层面也必须做相应的处理才能完成IRQ的分发处理,对于ARM内核来讲,IRQ只是一个中断向量,当IRQ中断请求时内核会跳到其在异常向量表中所处的位置去处理请求,ARM的启动代码必须在这个IRQ中断处理程序中分发处理才能分辨不同设备的中断请求,但有了上面的硬件的预处理过程,软件分发变得十分简单,一条语句就够了:即将AIC中断向量寄存器(AIC_IVR)里的值赋给PC就可以了。下面是AT91SAM9261的启动代码中定义的异常向量表:

Vectors LDR PC,Reset_Addr

LDR PC,Undef_Addr

LDR PC,SWI_Addr

LDR PC,PAbt_Addr

LDR PC,Dabt_Addr

; Reserved vector is used as size informaTIon for 2-nd level

; bootloader to use when copying program code to External SDRAM

IF :DEF:SIZE_INFO

DCD ||Image$$ER_ROM1$$RO$$Length||+\

||Image$$RW_RAM1$$RW$$Length||

ELSE

NOP

ENDIF

LDR PC,[PC,#-0xF20] ; Vector From AIC_IVR

LDR PC,[PC,#-0xF20] ; Vector From AIC_FVR

可以看到:IRQ对应异常处理指令是LDR PC,[PC,#-0xF20],当执行这条指令时,由ARM流水线结构,此时的PC = 0x18 + 2*4 = 0x20,因此执行之后PC被赋予地址:0x20 – 0xF20 = 0xFFFFF100里的内容,即IRQ向量寄存器AIC_IVR的内容,程序跳转到相应的中断例程中。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)