免费注册参加在线研讨会,学习如何分析、测量并最终解决音频系统的设计问题 (English only) 。

其中RPOT是可变电阻POT0和POT2设置对应的电阻值。

图1. 用DS3903构成的音频低通滤波器

电路的输入部分(C1、U1-POT1、U2A、R1和R2)是音量控制电路,它还用于将音频信号的直流偏置到VCC/2,使信号可以在不被钳位的条件下通过数字电位器和运放。任何供电电源下,电路能够处理最大信号摆幅,因此,该设计能够很好地工作在2.7V至5.5V VCC。输出直流电平保持在VCC/2,除非电路工作在正常输出以外,是电平偏移到不同的工作点。

对于已经限定工作范围的应用,可以去掉输入级电路,采用直接耦合的方式连接到滤波器。去掉输入电路后,输出信号只是经过截止频率为fC的双极点滤波器滤波后的信号,输入信号的直流成分将直接旁路到输出端。

更改电容或选择不同端到端电阻的数字电位器,该电路的截止频率可以设置到500kHz。

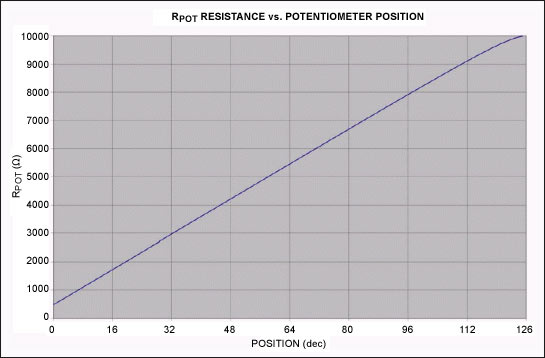

用于计算RPOT的数字电阻模型如图2所示,对于指定位置,相应的开关将闭合而其它位置的开关开路。电位器每递增一个单元位置,电阻将相应增加1 LSB (对DS3903,10kΩ/128 = 78Ω),最高抽头位置除外,最高抽头位置为电位器电阻的并联组合,会引起非线性。可通过下式计算RPOT:

其中:

- RLSB是数据资料电气参数表中的端到端电阻除以抽头数(a)。

- RW是数据资料电气参数表中的滑动端电阻。

- n是电位器的编程位置。

- a是数字电位器的总抽头数。

图2. 数字电位器的电阻模型

图3.

利用Audio Precision®测试设备对图1电路进行测试,可以得到图4至图6所示的衰减特性和THD+N性能。

图4.

图5.

图6.

数字电位器设计考虑为滤波电路选择数字电位器时需要考虑几个因素。

使用数字电位器的最大限制是电位器端点的电压,通常该电压必须保持在VCC和GND之间,以避免ESD结构内部的二极管将音频信号钳位。当VCC在规定的范围内(2.7V到5.5V)时,DS3903的ESD结构允许输入信号介于6V与GND之间,这一特性对于要求输入信号大于VCC的应用非常灵活。但是,在图1所示电路中并未处理6VP-P信号,因为运放电源低于6V时将会钳位信号。如果运算放大器能够用更高的电压供电,即可使用DS3903的大信号处理功能。

电位器抽头的变化形式(线性或对数)决定了电路截止频率的线性调节或对数调节形式。对于图1所示音频范围的滤波电路,为保证在40Hz与800Hz之间提供尽可能多的截止频率设置,采用线性电位器比较合适。

电位器的分辨率(如128或256抽头)决定了截止频率的调节精度,抽头数越多,截止频率的调节精度也越高。对于音频应用,不太可能使用64或128抽头以上的电位器来设置低通滤波器的截止频率。对于宽带应用可能要求更多的电位器抽头。

一些数字电位器采用非易失存储,能够在没有电源供电时保持抽头位置。这种特性可用于保存校准后的滤波器位置,而在上电时不再调整滤波器设置。易失电位器总是从一个预置位置启动,电路在被修改之前将一直保持默认位置。

数字电位器的端到端电阻和滑动电阻具有较宽的公差,图1所示电路中的两个电阻(POT0和POT2)则保持相等,因为这两个电阻制作在同一硅片上。电位器的实际阻值差别较大,通常端到端电阻的变化范围是±20%,但它们的相对值基本保持稳定。

另外,数字电位器内部也具有一定的寄生电容,这会限制最大截止频率。截止频率大于500kHz时,不推荐使用10kΩ的数字电位器,也不建议将50kΩ数字电位器用于100kHz以上的设计或将100kΩ的数字电位器用于50kHz以上的设计。对于音频应用,所选择的电位器能够提供足够的带宽,但对于宽带应用,必须慎重考虑这一因素。

运放选择该电路对于运算放大器的主要设计考虑是最小稳定增益和输入、输出电压摆幅。输入级接收信号并将其偏置在VCC/2直流电平,滤波器本身是单位增益放大器。为保证可靠工作,放大器必须是单位增益稳定;另外,还需选择具有满摆幅输入、输出的运算放大器,以处理接近电路供电电压的输入信号。

结论数字电位器可用来构建数控低通滤波器,本文中的双极点滤波器能够在音频应用中提供良好的性能,选择不同的电容、电位器值可以调整滤波器的截止频率,最高可达500kHz。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)