下面这个例子说明在用户的Flip-Flops设置初始值。大多数设计师这样写代码为的是仿真能够更加简便。否则当用户开始运行仿真的时候,用户设计中使用的寄存器等都处于一个不确定态。可以,按照例子来写的代码,可以让寄存器等有一个确定的初始值,处于一个确定态。

reg Q =1’b1;

always @ (posedge CLK or posedge RST )

begin

if (RST)

Q <= 1’b0;

else

Q <= D;

end

signal Q: std_logic:=‘1’;

FF: process (CLK, RST)

begin

if (RST = ‘1’) then

Q <= ‘0’;

elsif (rising_edge CLK) then

Q <= D;

end if;

end

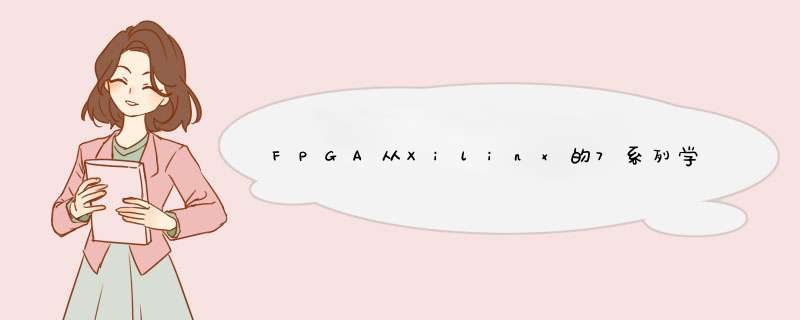

触发器中的Flip-flops和flip-flop/latches有着相同的控制信号,CLK,SR, CE等等。那么对用户来说最重要的事情就是尝试着减少用户设计中的控制信号的数量。用户需要加强对控制信号的行为的理解:所有Flip-flops和flip-flop/latches共享所有这些控制信号,这些控制信号主要是时钟,置位和复位。如果一个组中的一个flip-flop用了时钟使能信号,那么所有其他的Flip-Flop必须使用相同的时钟使能或者不用时钟使能。如果一个组中的一个flip-flop用了置位或者复位信号,那么所有其他的Flip-Flop必须使用相同的置位或者复位信号。

在同一个Slice中的Flip-Flops会在同一时间进入复位或者置位的状态。但是有一点需要强调一下:所有Flip-Flops都有自己单独的SRVAL属性,也就是说信号在统一复位的时候,可以有自己的值。

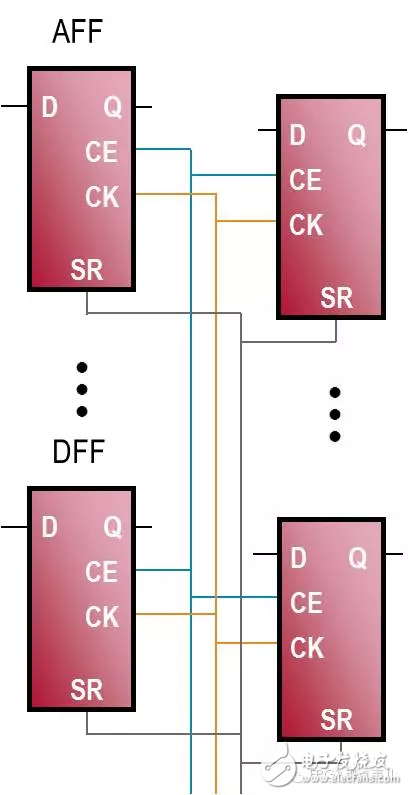

对于整个slice来说,使用它的设计者要切记注意控制信号,工具的推断功能非常非常重要的。特别重要的,因为触发器中每个切片将共享所有相同的控制信号,因为被占用后,其他和它使用不一致控制信号的触发器将无法使用剩下来的资源。那么对用户来说,设计要尽量使用少的控制信号:关键是要评估是否有未使用的寄存器的一些情况,如果有,就尝试使用相同控制信号。

另外,用户要记住控制信号的置位、复位、时钟使能信号是能连接到了LUT的输入端,而不一定是连接到相应的flip-flop的相对应的端口。不像老的FPGA的架构有独立的置位和复位信号端口,7系列的置位和复位端口没有独立的端口,但是可以只被被编程使用两个、一个或者一个也不使用。因此如果你想两个都是用的话,它必须用LUT去生成置位或者复位功能。以上说的都是同步的。置位或者复位信号可以被设置为异步信号。但是异步信号的置位或者复位信号端口不能使用LUT来生成,因此综合工具不可能使用LUT来实现、映射异步控制信号到LUT的输入信号中,它直接就会映射到寄存器的端口。

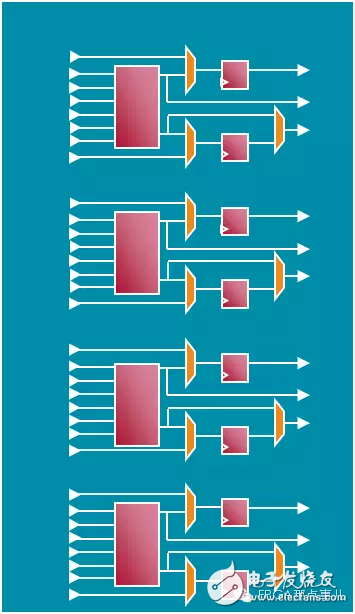

下图展示了工具如何通过使用同步置位和复位信号获得好处。工具转移置位和复位端口连接到LUT输入上,并将复位推断为同步,那么这些触发器可以被放置在相同的Slice。

这一功能可以通过使用综合过程的“Reduce ControlSets”属性来实现。

在这个例子中,三个触发器中的原始设计必须放在单独的Slice中,因为它们每一个使用不同的控制集合。所有三个触发器共享相同的时钟,但是第一个触发器没有置位/复位,第二个触发器使用“置位(set)”同步地将其输出设置为1,而另一个使用“复位(reset)”将输出重置为0。如果同步置位和复位功能被使用的LUT逻辑实现,那么所有三个触发器可以被置于同一个Slice中。整个实现过程,图例中显示的非常明显。那么用户可以看到增加了组合逻辑将一些控制信号放在未使用的LUT中去,却减少了Slice的总体的使用量。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)