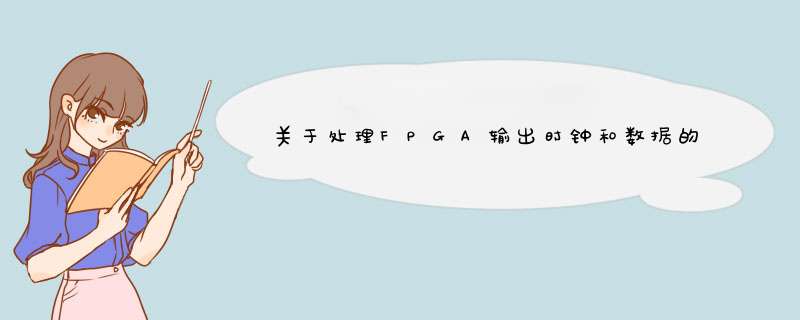

在FPGA的源同步的系统设计中,常常我们会碰到把随路时钟和数据一同输出的情形,如同下面的系统:

在这样的系统中,要求输出时钟o_clk和o_dat要由严格的相位对齐关系,一般是边沿对齐或者中心对齐。

那么如何才能保证上述相位对齐关系呢?

(1) 第一种做法(这样用的人不少)。

对于数据,通常用系统时钟打一拍或者不打拍,组合逻辑直接输出。

对于时钟,通常直接把FPGA内部的系统时钟赋值到IO PAD的输出管脚上。

如下所示:

assign O_CLK = sys_clk;

always@(posedge sys_clk)

o_dat= data_i;

// or assign O_dat =data_i;

这样的处理方式,需要约束文件里面通过offset out(UCF,SDC类似)约束输出时钟和数据的相位关系。

上面的处理方式其实对于FPGA不是最优选择。而且对于时钟直接赋值输出的处理方式,在某些器件上还会产生错误!更好的处理方式是下面第2中:

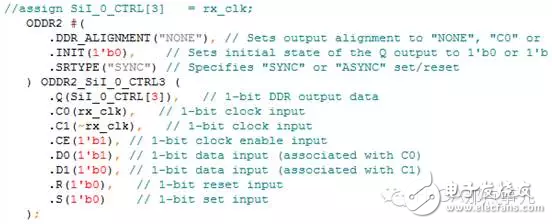

(2) 第二种做法

对于输出的数据,无论如何都要做到最终送到IO PAD时,是寄存器输出。这样我们可以把寄存器约束到IOPAD里面的IO LOGIC里面,保证所有数据输出延迟的一致性。

对于时钟,通过类似ODDR2的元件来产生一个时钟镜像输出:

这样的处理方式,不管是数据,还是时钟,实际上都是寄存器输出,而且都可以把它们放置到IO PAD里面,保证了时钟和所有数据相对相位关系的一致性。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)