关键词: AMC , ECP3 , FPGA

LatTIce公司的LatTIceECP3 FPGA系列可提供高性能特性如增强的DSP架构,高速SERDES和高速源同步接口。LatTIceECP3采用65nm技术,查找表(LUT)高达149k逻辑单元,支持高达486个用户I/O,提供高达320个18×18乘法器和各种并行I/O标准,主要用于对成本和功耗敏感的无线基础设备和有线通信。

2012-3-16 19:12:52 上传

FPGA器件的LatTIceECP3系列经过优化来提供高器件的性能,如增强的DSP架构,高速SERDES,和经济型FPGA架构,高速源同步接口。这种组合是通过器件架构的进步,和65nm技术的使用而完成的,这就使得其设备适合高容量、高速度和低成本的要求。 LatticeECP3器件系列使得查找表(LUT)的容量扩大至149k逻辑单元,并支持多达486个用户I/ O。

LatticeECP3器件系列还提供了多达320个18×18乘法器和广泛的并行I/O标准。LatticeECP3 FPGA架构进行了优化,目的是提高性能和降低成本。LatticeECP3器件采用可重构SRAM逻辑技术,并提供了深受欢迎的构件,如基于LUT的逻辑,分布式的嵌入式存储器,锁相环(PLL),延迟锁定环(DLL),预制的源同步I-/ O支持,增强的sysDSP片以及先进的配置支持,包括加密和双启动功能。

在LatticeECP3系列上应用的、预设计的源同步逻辑支持广泛的接口标准,包括DDR3,XGMII和7:1 LVDS。 LatticeECP3器件系列还具有专门用于PC功能的高速SERDES。高抖动容限和低传输抖动使得SERDES+PCS块可以进行配置,以支持流行的数据协议,包括PCI Express,SMPTE,以太网(XAUI,千兆以太网和SGMII)和CPRI。发送预加重和接收均衡设置使得SERDES非常合适各种形式的媒体传输和接收。

LatticeECP3器件还提供灵活,可靠和安全的配置选项,如双启动,比特流加密和TransFR现场升级功能。Lattice的ispLEVER设计工具套件,通过使用LatticeECP3 FPGA系列,可以使得大型复杂的设计更加有效地实施。支持LatticeECP3的综合资料库可以提供给工程师,以便逻辑综合工具的使用。

ispLEVER工具采用了结合型工具输出(避免板上平面图设计工具的制约)来设计LatticeECP3器件的路线和布局。ispLEVER工具从路由中提取时序,并诠释成设计,用以验证时序。Lattice公司为LatticeECP3系列提供了许多预先设计的IP(知识产权) ispLeverCORE模块。采用这些可配置的软核IP作为标准化的模块,设计师们可以没有后顾之忧地专注于他们的独特设计,以增加效率。

图1 Lattice ECP3 AMC评估板外形图

LatticeECP3 FPGA主要特性

更高的逻辑密度,提高了系统集成度

•17k~149k的LUT

•133~586个I / O

嵌入式SERDES

•150 Mbps~3.2 Gbps用于Generic 8b10b,10位SERDES和8位SERDES模式

•其他协议每通道数据传输速率230 Mbps~3.2 Gbps

•每个设备最多16个通道,PCI Express,SONET / SDH,以太网(1GbE,SGMII XAUI),CPRI,SMPTE 3G和Serial RapidIOsysDSP

•全级联片结构

•12到160片高性能乘法和累加

•强大的54位ALU *** 作

•时分复用MAC共享

•舍入和截断

•每片支持

-半个36×36,两个18×18,或四

个9×9乘法器

-先进的18×36 MAC和18x18乘法乘法累加(MMAC) *** 作灵活的内存资源

•最多6.85Mbits的sysMEM 嵌入式RAM块(EBR)

• 36k~303k位分布式RAMsysCLOCK模拟PLL和DLL

•两个DLL,和每个设备多达10个锁相环预加工源同步I/O

• I/O单元里的DDR寄存器

2012-3-16 19:12:52 上传

下载附件 (18.26 KB)图2 Lattice ECP3 AMC接口板外形图

•专用的读/写平衡功能

•专用齿轮逻辑

•源同步标准的支持

- ADC/DAC,7:1 LVDS,XGMII高速ADC/ DAC器件

•专用DDR/DDR2/DDR3内存,支持DQS

•校正输出可选的符号间干扰(ISI)可编程sysI/O的缓冲区支持多种接口

•片上终止

•可选输入均衡滤波器

• LVTTL和LVCMOS33/25/18/15/12

• SSTL 33/25/18/15 I,II

• HSTL15 I 和HSTL18 I,II

• PCI和差分HSTL,SSTL

• LVDS, Bus-LVDS,LVPECL,RSDS,MLVDS灵活的设备配置

•专用库用于配置I/O

• SPI引导闪存接口

•双启动图像支持

•从SPI TransFR的I/O用于简单现场更新

•软错误检测嵌入宏系统级支持

• IEEE 1149.1和IEEE 1532兼容

• Reveal逻辑分析器

• ORCAstra FPGA配置实用程序初始化与一般使用的片上振荡器

• 1.2V核电源

Lattice ECP3 AMC评估板

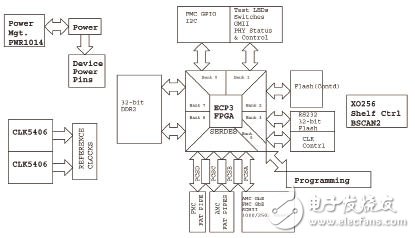

LatticeECP3高级夹层卡(AMC)评估板可以使设计师们在AMC系统环境中对LatticeECP3高速SERDES收发器的功能进行调查和实验。LatticeECP3 AMC评估板可以协助设计师们进行快速的原型设计,并测试他们的设计。该评估板具有PICMG AMC R2.0 AMC的外形尺寸规格,可以使用户在现场系统评估。本用户指南要参考评估设计教程来使用,以更好地了解LatticeECP3 FPGA。

2012-3-16 19:12:52 上传

下载附件 (18.13 KB)欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)