作者:Steve Leibson, 赛灵思战略营销与业务规划总监

上周在X-fest San Jose大会上,我结识了安富利电子公司负责全球技术市场和数字信号处理业务的主管Luc Langlois先生,并且从他那里学到了一个小笑话。让FPGA直接转换和处理复用的高频(GHz)RF(射频)信号的方法是从高速的ADC接口获取复用高频(GHz)的采样信号流,将它传输到一个多相通道里进行并行处理。

你需要数学来理解一个公式—— 数学包含了等式定理(heterodyne + baseband filter = bandpass filter + heterodyne)和一些恒等式。对于数学我不怎么在行,所以在这里我就不去尝试解释这个等式了,否则我一定会弄错的。

然而我将有机会参与部分系统设计,当你完成数学公式的证明后你也需要了解一下系统设计的一些细节。

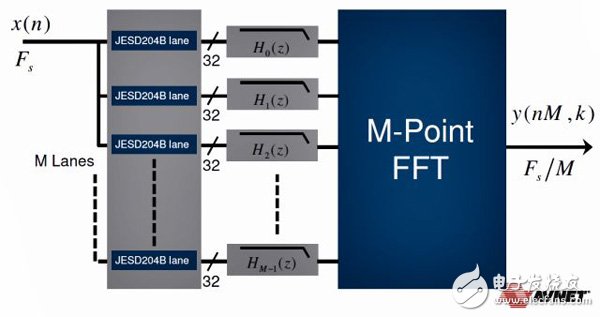

如果你想实现一个多相的传输信道,你所需要做的就是需要一个转换器将高速的采样数据流转换成低速的数据流,使用一个低通的滤波器过滤每个信号流,然后对过滤后的信号流进行快速傅里叶变换(FFT)处理 ,这就是数学定理公式所描述的意思。

很简单,是不是?

除了以上所说的,转换器的转换速率 要与ADC的采样速率相匹配,你将不需要再FPGA的外部搭建一个转换器,因此就算搭建了一个外部转换器,也不能满足高速的采样速率。幸运的是带有可编程的JESD204B串行接口的ADC内部已经实现了一个转换器,这就是上面提到的那个小笑话。

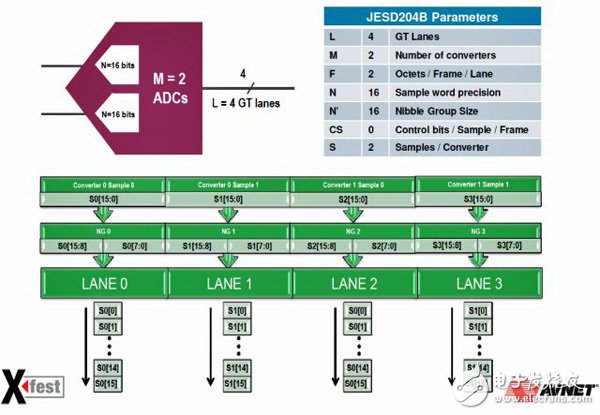

就采样信号而言,下图展示了四通道的JESD204B接口所输出的信号信息:

从上图可以看出转换是免费的,使用JESD204B接口将数据转换到四个通道里面,也就是说你将1Gsanples/sec的信号流转换成四个250Msample/sec的信号流,用于在较低的时钟速率下进行滤波和并行处理。这样你就可以将设计中头疼的问题解决了,而且不会消耗FPGA的LUT(查找表)资源。

这是不是有一些神奇?

下面的模块图是利用这项技术实现的全速多相信道信号传输处理流程图:

这些信息来自X-fest课程,名称是“High-Speed Digital Signal Processing in UltraScale FPGAs”(在UltraScale 系列FPGA内部的高速数字信号处理),如果你想获得一些这个硬核设计的培训机会,现在仍然有时间进行登记,参与X-fest大会。

Avnet X-fest系列会议正在北美地区举办,可能哪一边就会到你附近的城市,点击这里查看具体信息。

欧洲之行会在十月份启动,点击这里产看日程和城市安排信息。

要了解亚洲地区的日程安排信息,点击这里。

原文链接:

? Copyright 2014 Xilinx Inc

如需转载,请注明出处

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)