人工智能的整个产业链从生产到应用,无论是在云端的训练、推理、分析,还是终端的人机交互、推理,需要非常强的算力。

相比其他CPU、FPGA、GPU等类型的芯片,ASIC在计算效能、大小、成本等方面都有极大优势,未来随着通用AI指令集架构的开发,预计会出现最优配置的AI计算芯片。

“几个月的电费省下来就可以定制芯片了”

现在视频非常火,从2K、4K到8K不断升级,一些最初用CPU和GPU的厂商,最近也可开始转向ASIC。

“ASIC和CPU的视频转码能力差了好几个等级。”芯原股份创始人、董事长兼总裁戴伟民博士指出。

“芯原的定制化ASIC和CPU方案相比,尺寸小很多,不仅功耗是1/3,转码能力是6倍,做成系统之后转码能力可以提高36倍,功耗降低50%。”戴伟民博士透露,“有的大供应商告诉我,几个月的电费省下来就可以定制芯片了。”

但是,尽管有ASIC有这么多优势,初始设计投入却很大。

ASIC高设计成本催生“轻设计”模式

随着先进工艺的发展,单位算力的成本逐步下降,使面向边缘计算的AI处理器更具成本效益。例如,基于16nm工艺节点的每TOPS的成本为0.67,基于3nm工艺节点的每TOPS的成本就只有0.67,基于3nm工艺节点的每TOPS的成本就只有0.06了。

但,ASIC的设计投入也越来越大。

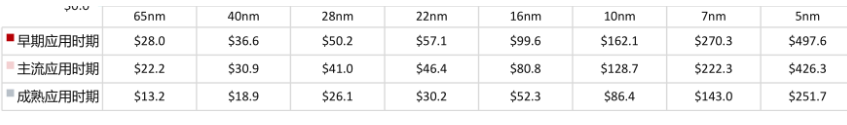

以工艺制程处于主流应用时期的设计成本为例,工艺节点为28nm时,单颗芯片设计成本约为0.41亿美元,而工艺节点为7nm时,设计成本则快速升至约2.22亿美元。

“其中早期使用和成熟期使用的成本相差一倍以上,但成熟期的使用成本仍非常昂贵。”戴博士表示。

半导体行业有上行也有下行,这是周期性的。很多公司都在低潮时投入,但是低潮时很可能物力不够,要提高效率就要尝试外包,特别是一些通用IP。

值得一提的是,芯原在全球IP公司排名第七,中国第一,但是和全球前六大IP厂商相比,芯原的IP种类是最多的。现在900多名员工中80%是研发工程师。

“最近发现很多机遇,特别是疫情期间大部分国家都没有复工,芯原大部分员工在中国很早就复工了,所以客户需求不断在增加。”戴博士表示,“芯原的业务模式的有着‘逆周期’的属性,除了海外客户的增加,设计服务业务的需求也在扩张,同时这也是收购 IP 和 IP 公司的好时机。”

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)