同步RS触发器在R、S同时为1且同时失效后,触发器状态不确定,说明其功能仍不完善。D触发器针对这一问题作出改进,解决了触发器状态不确定的问题。

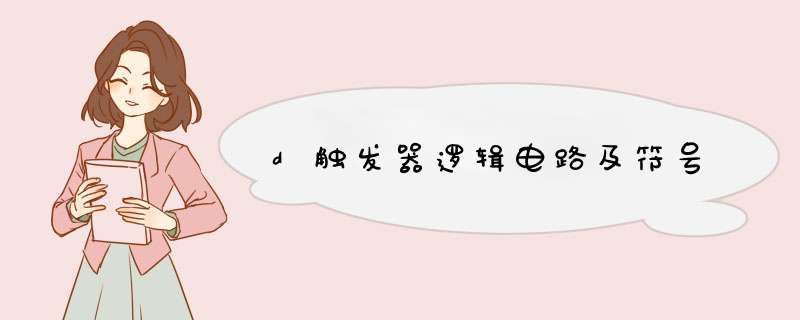

由于只要令R、S不同时为1,触发器就不会出现状态不稳定,最简单的方法就是令S=/R,此时仅将S作为输入端(用D表示),就得到了D触发器。仍然是由RS触发器演变而来,是RS 触发器S=/R的特例,其电路结构和逻辑符号如图所示。

图 同步D触发器

工作原理如下:

①CP=0期间,与非门G3、G4被封锁,/RD=1,/SD=1。因此,无论输入信号R、S如何变化,都不会影响触发器的输出Q和/Q,即触发器状态保持不变。

②CP=1期间,与非门G3、G4打开,触发器输出状态随D而变化,完成置0、置1和保持等三种逻辑功能。

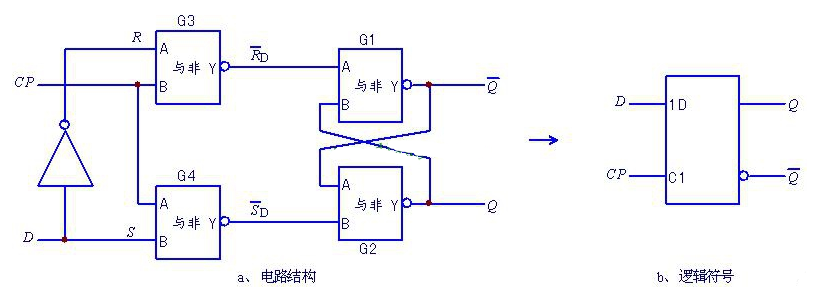

CMOS主从D触发器电路组成及逻辑符号

图 CMOS主从D触发器

(a)逻辑电路 (b)逻辑符号

CMOS集成D触发器特点:

· 结构上,是主从触发器,由两个带使能端D触发器构成;

· 性能上,是上升沿触发的边沿触发器,由上升沿前的D输入和当时的状态决定输出如何翻转;

· 虽然是主从触发器,但是没有一次翻转的问题。

· 异步置1置0信号时高电平有效。

d触发器逻辑电路及符号详解

一。电路组成及其工作原理

(一)电路组成及逻辑符号

1.电路组成

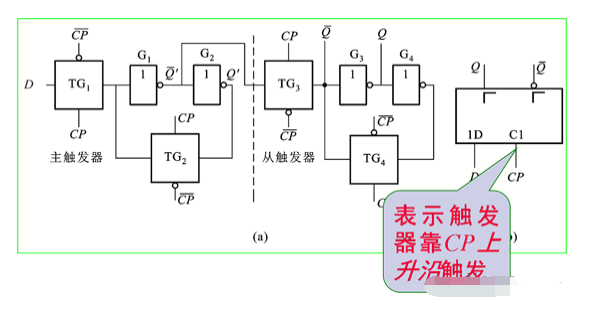

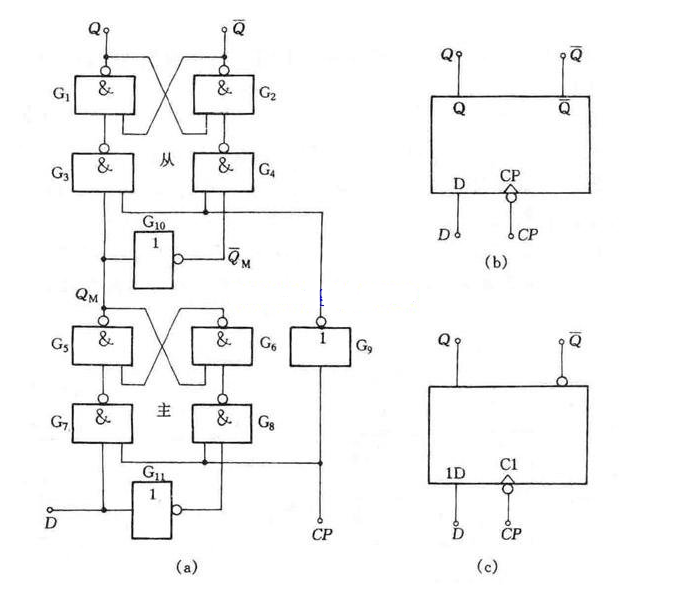

图4.4.1 边沿D触发器

(a)逻辑电路 (b)曾用符号 (c)国标符号

图4.4.1所示是用两个同步D触发器级联起来构成的边沿D触发器,它虽然具有主从结构形式,但却是边沿控制的电路。

2.逻辑符号

图4.3.1(b)所示是曾用逻辑符号,图4.3.1(c)所示是国家标准规定的逻辑符号.CP端的小圆圈表示下降沿触发。

(二)工作原理

图4.4.1(a)所示为具有主从结构形式的边沿D触发器,由两个同步D触发器组成,主触发器受CP *** 作,从触发器用。。管理。

1. CP=0时的情况

CP=1时,门。。被封锁,门。。打开,从触发器的状态决定于主触发器,…输入信号D被拒之门外。

2. CP=1时的情况

CP=1时,门。。打开,门。。被封锁,从触发器保持原来状态不变,D信号进入主触发器。但是要特别注意,这时主触发器只跟随而不锁存,即。。跟随D变化,D怎么变。。也随之怎么变。

3. CP下降沿时刻的情况

CP下降沿到来时,将封锁门。。打开门。。主触发器锁存CP下降时刻D的值即。。随后将该值送入从触发器,使Q=D,。。

4. CP下降沿过后的情况

CP不降沿过后,主触发器锁存的CP下降沿时刻D的值显然将保持不变,而从触发器的状态当然也不可能发生变化。

综上所述可得

式(4.4.1)就是边沿D触发器的特性方程,CP下降沿时刻有效,注意,式的的。。只能取CP下降时刻输入信号D的值。

与主从触发器中情况一样,在边沿D触发器中也设置有异步输入端…用于直接复位,称为直接复位端或清0端,。。用于直接置位,叫做直接置位端或置1端。图4.4.2所示是其逻辑符号。

图4.4.2 带异步输入端的边沿D触发器的逻辑符号

(a) 曾用符号 (b)国标符号

逻辑符号中:异步输入端的小圆圈表示低电平有效,若无小圆圈则表示高电平有效;CP端有小圆圈表示下降沿触发,若无小圆圈则表示上升沿触发

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)