数据采集是工业测量和控制系统中的重要部分。它是测控现场的模拟信号源与上位机之间的接口,其任务是采集现场连续变化的被测信号。系统应将所采集的模拟数据信号尽可能真实、不失真地显示给控制人员。

随着计算机技术和EDA技术的发展,由于复杂可编程逻辑器件(CPLD)具有高集成度、小体积、低成本、低功耗以及高稳定性等诸多优点而广泛使用到诸如传统工业控制等各个领域。基于ISA的接口电路,其布线要求远没有PCI或USB接口板高。由于它能够提供16位I/O *** 作,对I/O的直接读写可以完全不考虑复杂的驱动程序和应用程序,因而在ISA总线上开发接口电路目前仍是首先考虑的方法。因此,这里提出一种基于CPLD和ISA总线的数据采集系统设计。

1 系统硬件设计

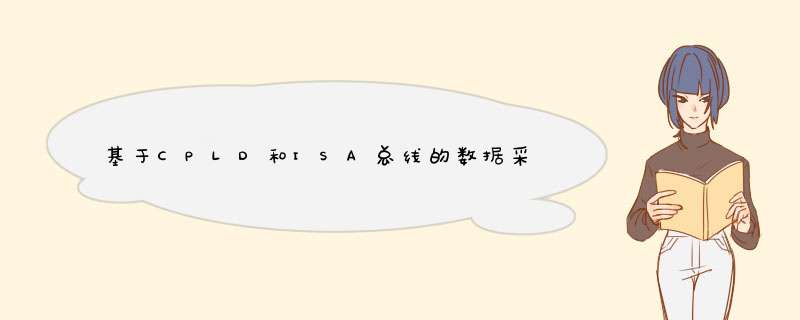

数据采集系统的硬件电路主要包括:CPLD逻辑控制电路、8254定时器电路、A/D转换电路。该系统硬件设计框图如图1所示。

1.1 CPLD逻辑控制电路

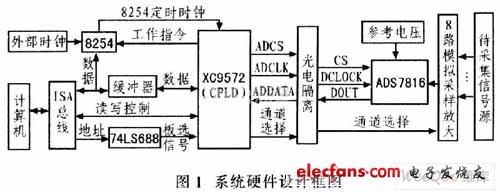

该系统使用XC9572作为主控器件。XC9572是一款高性能可编程逻辑器件,内含4个36 v 18功能模块,具有l 600个可用系统门。ISA总线上的地址、控制指令和数据被送进CPLD,经处理后送到相应电路中。由A/D转换电路得到的数据也返回到CPLD进行处理,并经ISA总线送至计算机中。

图2为数据采集系统的逻辑控制电路,Ul是数据缓冲器74HC245,由lSA总线的读/写信号(IOR/IOW)和板卡选择信号(BSEL)决定数据的流向。比较器74LS688和XFl组成板卡选择信号发生电路。通过在XFl上的跳线可确定采集系统板的基地址。该系统基地址设置为280H。

ISA总线上的读写信号,经缓冲器的数据信号(LADO~LAD7),地址信号(A0~A3)均与XC29572相连,CPLD发送A/D转换器的片选信号(ADCS)、A/D时钟信号(ADCLK)以及通道选择信号(CHA0~CHA2)。

1.2 8254可编程定时器电路

8254可编程定时器内部具有3个独立的16位减法计数器,它可由程序设置成多种工作方式,有6种可选工作方式。计数器按照设置各工作方式寄存器中控制字工作,按十进制计数或二进制计数,最高计数速率可达10 MHz。

该数据采集系统需要由8254提供AD转换电路的时钟信号和片选信号,通过改变8254的控制字改变数据采集系统的转换频率。8254定时器的输入时钟由外部晶振提供。定时器和定时器的输出信号直接送入可编程逻辑器件XC9572,经处理后提A/D转换电路使用。上位机写入的控制字经ISA总线送至8254,同时XC9572给8254提供必要的控制信号,如:8254读/写信号、片选信号、地址信号等。

假设系统的外部时钟为2 MHz,如果需要8254的定时器0输出一个频率为l MHz,占空比为50%的时钟,则8254的定时器控制字可设置为:D7~D0=00110110,其中,D7D6=00,表示选择定时器;D5D4=11,表示先读/写低8位,后读/写高8位数据;D3D2Dl=011,表示工作方式3,方波发生器;D0=0,表示二进制计数。

1.3 A/D转换电路

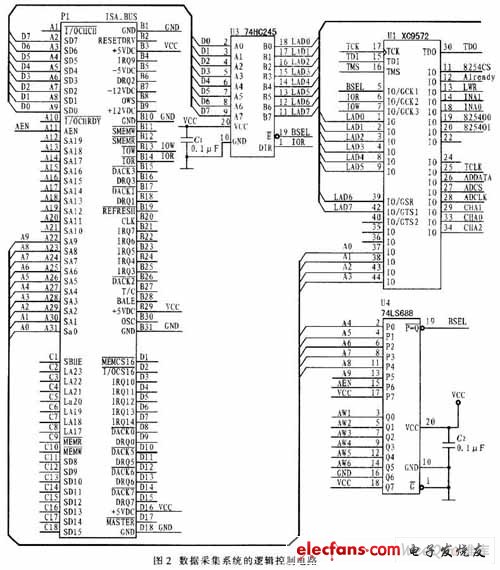

A/D转换电路完成数据采集和转换,主要包括MD转换和模拟信号采样两部分电路。

8通道模拟采样开关ADG508用于采样模拟信号。由CPLD送来的通道选择信号(CH0~CH2)用于选择输入的通道号。被选通的通道采样得到的模拟信号送给ADS7816的IN+端,进行AD转换,如图3所示。

A/D转换电路采用TI公司的ADS7816,该器件是12位串行A/D转换器,采样频率高达200 kHz,转换所需时间短,转换精度高,输出形式为位串行,因此在对ADS7816进行读数据 *** 作时需注意数据转换过程中的时序。

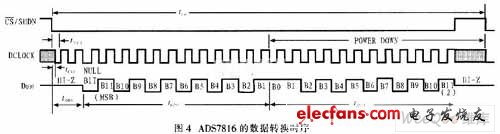

图4是ADS7816的数据转换时序。当ADS7816的片选端下降沿到来时,开始启动一次A/D转换,保持转换时钟输入和片选信号低电平,最初的1.5~2个时钟时间里,完成模拟信号的采样,这段时间ADS7816的输出呈高阻状态(HI-Z)。紧接着的1个时钟周期里,DOUT输出1个空位(NULL BIT)。随后,ADS7816在12个连续的时钟周期内把12位的A/D转换结果输出,其中先输出最高位(MSB),最后输出最低位(LSB)。如果12位数据送出后仍有转换时钟且ADS7816的片选仍保持低电平,那么转换器会从最低位起逐位重复输出之前转换的结果。当下一个片选信号的下降沿到来时,A/D转换器开始启动下一次A/D转换。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)