电子发烧友讯:在未来的半导体IC设计领域,过多的消耗能耗直接制约着半导体的细微化发展,成为研究未来超级计算机的移动器件微型化的一大障碍。

基于此,我们有必要根植于物理化学原理探讨IC设计技术领域,以期帮助解决工程师在进行创新设计中受益和希望以此推动芯片工业的复兴。

本文将分五个章节论述如何在未来的IC设计中有效降低能耗的五个最为有效的方法。目前它们正被广泛利用并实践发展着,相信在未来十年内这五个方法能在各领域发挥重要作用。其余部分电子发烧友将于近期陆续发布,敬请留意。

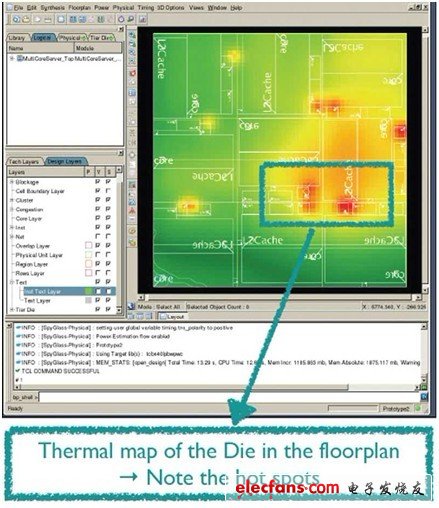

设计之初就能准确预估设计电路中存在及潜在能耗热点

一、拥抱协同设计

电子设计自动化工具能使得整个团队在进行前端设计时对低功耗进行优化。事实上,最低功耗和SoC(片上系统)的开发者一开始就拥有先天性的优势,因为他们不但有最佳的架构和材质,而且在协同封装,电源,RF电路和软件就可达到功耗的最小化,而无需通过衰减其性能和成本去完成。

德州仪器(Texas Instruments)设计及EDA部门主管David Greenhill就曾指出,低功耗必须通过技术,设计方法学,芯片架构和软件共同建立起来。

德州仪器运用首创技术来对各个子系统的低功耗器件进行优化,如利用自身工艺技术来使脱模漏电和主流子性能达到平衡,或使用电源和频率去规定节能 *** 作指标。

刚开始的第一步必须得弄清楚产品的性能和能耗的要达到的预期目标。一旦这些目标被确定后,按照提供的性能要求即可进行设计生产环节,从而省去了过度依赖器件的功耗而造成的成本预算,德州仪器28纳米平台经理Randy Hollingsworth表示。

EDA工具一向被用来获取低功耗的主要途径,但由于传统的EDA工具只在设计周期的末端才能对功耗的预估得比较精确,因此,有时这些工具在设计的整个流程中会被反复使用。对于未来的IC,能耗估算应当尽可能早的在设计周期的早期就能精确计算出来。

少数该领域专业设计工具供应商Atrenta公司已获得相关技术突破。譬如,旗下一款名为“电源望远镜”的EDA设计工具,该平台使用RTL(寄存器传输)技术对所有其他主流EDA工具在设计的早期就能对能耗进行预测,减少和核实描述。

Atrenta的工程部高级经理Peter Suaris指出,今天,工程师想在设计流程的早期完成对能耗的预估,就不能再等到设计末端来对其进行功耗预测了。现在你需要将能耗的协同设计提高到RTL(寄存器传输)级,这样改变你的设计将有助于在一开始为有效的能效设计打下坚实的基础。

Atrenta估计它的专业电源保护工具能将能耗预算降低到20%左右,能耗下降50%。

--未完待续...

本文系电子发烧友原创,转载请注明出处!

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)