前言

随着SERDES应用越来越多,速率也越来越高,SI的问题渐渐变得越来越重要,它对PCB设计,SERDES参数优化都有着非常重要的指导作用。而器件选型也往往以SI仿真开始。

但是在仿真时,工具会让用户自己设置一些信息,比如抖动,摆幅,预加重等等。摆幅和预加重之类都可以在手册里找到。但抖动的设置却没有一个明确的指导。而且不同抖动设置的会得到完全不同的结果。所以错误的设置往往会误导我们的设计和优化。特别在器件评估阶段还会决定器件选型的成败。

这篇短文就是给大家仿真中设置抖动一个简单的指导。

抖动

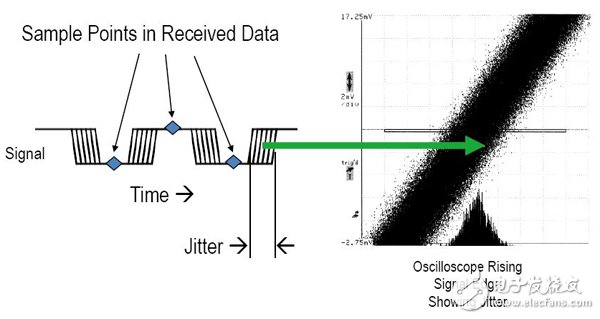

简单而言,抖动就是信号的沿对理想位置偏移。在示波器上,如果没有抖动,我们可以看到信号沿应该是一条清晰的线。但是由于抖动的存在,我们在沿上看到的是模糊的一片。

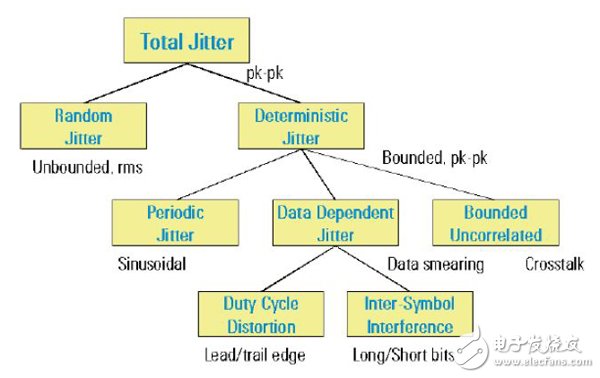

根据抖动的特性及其形成原因,抖动可以分成2种:随机抖动(RJ: Random Jitter)和确定抖动(DJ: DeterminisTIc Jitter)。

随机抖动RJ

随机抖动是由热噪声、散粒噪声等随机噪声引起。它的分布符合高斯分布。由于高斯分布的尾部扩展到无穷大,RJ的峰峰值没有边界。而RJ的均方根(RMS: Root Mean Square)收敛到高斯分布的宽度上。所以 随机抖动一般测量的都是其均方根值,以ps RMS或UI RMS为单位。

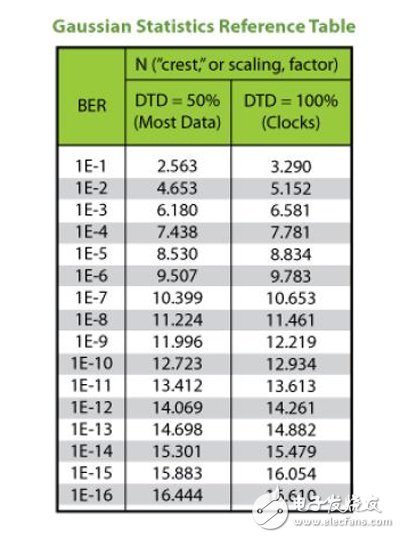

当我们要在RMS和峰峰值间近似转换时,就需要有一个转换系数,它根据不同的误码率有对应的值,如下表所示:

确定性抖动DJ

确定性抖动有3个基本的分类

数据相关抖动(DDJ: Data Dependent Jitter)

1. 占空比失真 (DDC:Duty Cycle DistorTIon)

2. 码间干扰(ISI: Inter-Symbol Interference)

周期性抖动 (PJ: Periodic Jitter)

有界不相关抖动 (BUJ: Bounded Uncorrelated Jitter)

周期性抖动PJ是在某个周期或频率上重复出现的抖动信号,相当于对信号有一个调频。所以会看到周期性地出现信号周期的变大和变小。

有界不相关抖动BUJ主要是由电磁干扰(EMI)、串扰引起。其中串扰是BUJ的主要成因。由于串扰形成的随机性,BUJ是有界的,但他和数据模式无关。顺便说一下,这个抖动在接收侧是无法补偿的,在测试接收抖动容忍度时,插入的就是BUJ。

数据相关抖动DDJ由于电或光系统的“记忆”效应,当前bit的跳变时刻会受到前面bit跳变时刻的影响而引入的。它和数据的模式(pattern)相关,其中和游程(Run Length)密切相关,另外一个是占空比失真。同时DDJ还和信号经过的信道或媒质的冲击/阶跃响应有关。由于不同数据模式所带不同的游程使得脉冲跳变沿不均匀,使得出现了ISI。最大的干扰来自于短脉冲和与其极性相反的长脉冲之间的干扰,反之亦然。

确定性抖动测量的是峰峰值,以ps或UI为单位。

为了方便理解,下面是抖动的整个分类图:

对于抖动的详细说明,有很多资料可查,所以这里只是简单说明一下,以方便理解后面的正题。

在XILINX的IBIS-AMI模型里对抖动的处理如下:

1. PJ、DCD等DJ这些SERDES固有的抖动元素在建模时都已经包含在内,所以在EDA/仿真工具里,所以相应的值可以放心地设成0;

2. RJ是需要用户自己设置的;

3. ISI和线路相关,所以在这个DJ元素会在仿真中体现,不需要在TX侧设置(否则会重复计入)。

仿真中抖动的设置

抖动设置

在XILINX的每款芯片出来后,都会有特性报告。在仿真里,我们需要用的是Generic CharacterizaTIon Report,因为这是大批量测试的结果。

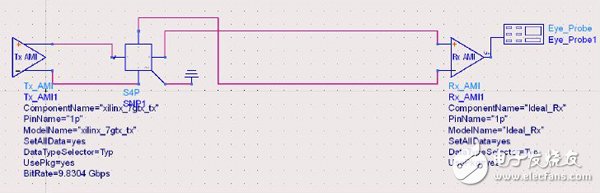

在这里我们以ADS上仿真GTX为例做说明,线速率是9.8304Gbps。

在仿真中,我们需要看TX信号经过一段PCB走线后的眼图。需要说明一点的是,在ADS中,用bit-by-bit模式是符合仿真结果的。特别当我们在线路中间加上EYE_PROBE_DIFF时,STATISTIC模式的结果是不可用的。

接收侧的模型是一个IDLE_RX。它没有均衡设置,只相当于是一个终端匹配。这样是为了能够客观显示远端眼图,而不是经过RX均衡后的眼图。

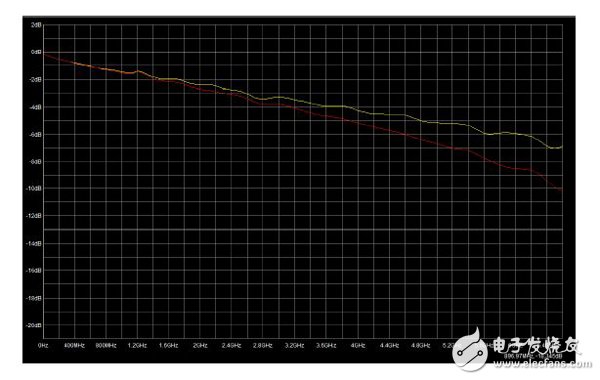

从通道(包括FPGA封装和PCB走线)的S参数看,在4.9152GHz上的插损是

1. 单端(红色): -6.5dB

2. 差分(黄色): -5.1dB

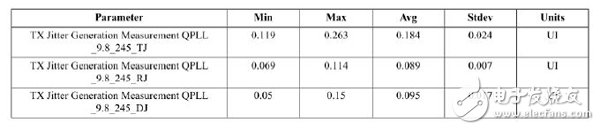

从K7 GTX的Generic Characterization Report,我们可以看到发送侧在9.8304Gbps速率下的发送抖动。

表格中的RJ是峰峰值。

不管是TJ还是DJ, RJ, 都有MIN和MAX值。但不是简单的把DJMAX 和RJMAX简单相加就是TJMAX。这些都是各自的最大值,但不是最大DJ的通道有最大RJ。从表格里值简单相加也说明不是这样的。

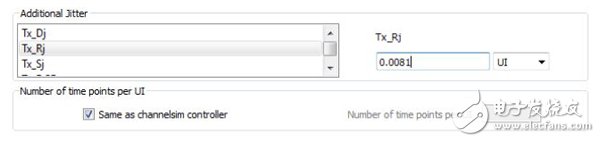

所以我们在选择参数是,就选最大值MAX, 0.114 UI。

在ADS的设置里,RJ是RMS值。由于我们设置的误码率是1E-12, RJ需要除以系数14.069:

0.114/14.069 = 0.0081 UI

前面说到,ISI的的原因是不均匀的脉冲沿经过PCB走线后由于其“记忆”效应导致。这是信号经过传输线后的必然效应。所以这个不能设置在发送侧的DJ里,否则会重复计算ISI的值。

仿真结果

由于信号需要走一段PCB,我们在发送侧还设置了预加重。

TXPRECURSOR = 3 (0.68dB)

TXPOSTCURSOR = 8 (1.94dB)

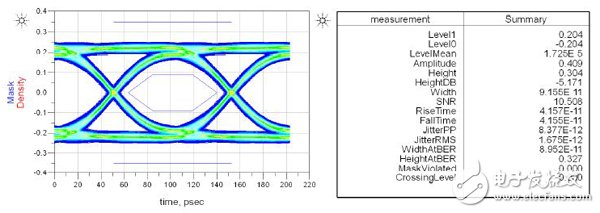

下面是摆幅为677mV时的结果。

由于PCB板子的原因,远端眼图的抖动大于特性报告的值。这是可以理解的。

总结

在SERDES的仿真里,抖动的正确设置至关重要。

在XILINX SERDES的IBIS-AMI模型里,已经包括的DJ的主要要素,而ISI是信号经过传输线引入的。所以在仿真时,DJ设成0, RJ则是SERDES的Generic Characterization Report的最大值以得最坏结果。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)