摘 要:在基于FPGA芯片的工程实践中,经常需要FPGA与上位机或其他处理器进行通信,为此设计了用于短距离通信的UART接口模块。该模块的程序采用VHDL语言编写,模块的核心发送和接收子模块均采用有限状态机设计,详述了各子模块的设计思路和方法,给出了它们的仿真时序图。综合实现后,将程序下载到FPGA芯片中,运行正确无误。又经长时间发送和接收测试,运行稳定可靠。相对参数固定的设计,该UART的波特率、数据位宽、停止位宽、校验位使能及校验模式选择均可以在线设置,为FPGA与其他设备的通信提供了一种可靠途径,具备较强的实用价值。

0 引 言通用异步收发器(universal asynchronous receivertransmitter,UART)尽管自20世纪70年代就已出现,但因其简单可靠,目前仍是一种使用广泛的串行通信接口。各种微处理器,不论是单片机,还是DSP、ARM,UART都是基本外围模块。许多场合如系统监控、数据采集都要用到串口通信[1-3],甚至要用多个串口,如开发串口服务器[4-6]。此时通常采用专用芯片,如16C554、VK3224等扩展串口。专用芯片使用简单,然而缺乏灵活性,同时专用芯片集成的串口数量也有限,有时需使用多个芯片才能满足要求[5],增加了系统的复杂度,降低了可靠性。

FPGA(field programmable gate array)作为一种可编程芯片,其资源丰富、工作效率高,常用于高速数据采集、算法的高速并行执行[7-8]。用户可通过硬件描述语言或电路原理图,设计出个性化的高性能电路模块,具有设计灵活,升级方便的优点。

在基于FPGA的工程实践中,常需要其与串口设备通信,但在Xilinx现有的开发环境ISE中没有相关的IP核。目前也有使用FPGA设计UART的例子[9-13]后,但有的参数固定,缺乏通用性。本文设计和实现了参数可在线配置的UART接口模块,为FPGA与其他设备通信提供了一种可靠途径。

1 UART串行通信简介标准的RS232接口常采用DB-9连接器,其有2根数据线,6根控制线,1根信号地线。本文设计的UART符合RS232串行通信标准,但在实际中,RS232标准中诸多控制信号使用较少,故文中的UART只使用其中的3根信号线,即TXD、RXD和信号地,这也是很多微处理器UART模块所采用的信号线。

UART属于异步通信接口,通信双方需约定好波特率。国际上规定了一系列标准的波特率,如9 600b/s、19 200b/s、115 200b/s等。UART每一数据帧,依次由起始位(1位)、数据位(5~8位),奇偶校验位(可选的1位)以及停止位(1~2位)组成。其中数据位部分是从最低位先开始传送的;奇偶校验位是对1帧数据中的数据部分和校验位计算,使‘1’的个数满足奇数个或偶数个。当UART空闲时,收发引脚RXD与TXD均是高电平。一旦需要发送数据,则首先向TXD引脚输出低电平作为起始位,表示1帧数据的开始。而在接收数据时,检测到起始位将启动一次数据接收流程。

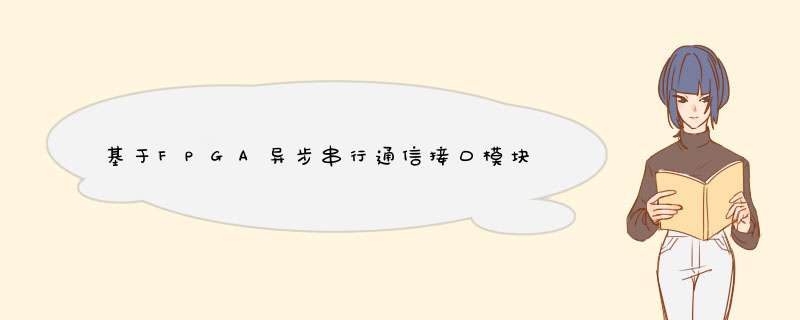

2 系统设计本文设计的UART通信接口主要由波特率产生模块、发送模块、接收模块以及微处理器接口模块组成。各模块使用VHDL语言来表述,模块之间的信号连接是通过顶层文件中的元件例化语句实现。

整个设计的结构框图如图1所示。设计和实现的UART通信模块主要功能如下:

1)实现了串行数据的发送和接收。

2)停止位可设置(1位或2位)。

4)波特率可配置。标准的波特率系列中从9 600~115 200b/s均可设置,同时还支持自定义的波特率。

5)设计了微处理器接口,通过接口可访问UART内部寄存器,配置UART参数,读写收发数据。

该UART 通信接口包含2 个数据缓冲寄存器(TxHolder和RxHolder)、3 个控制寄存器(UartCon、UartBaud及UartIntEn)、3 个状态寄存器(UartState、UartError、UartIntPend)。考虑到需要在线更新UART参数,设计UartCon与UartBaud为双缓冲寄存器。第一级缓冲用于存储外部处理器写入的配置数据,第二级缓冲即用于设置UART内核。当UART内核空闲时,才将第二级缓冲内容更新为第一级缓冲内容,防止破坏收发中的数据。

3 UART各模块的设计下面详细介绍UART各模块的设计思路和方法,同时给出了主要模块的行为仿真时序图。

3.1 波特率发生模块波特率发生模块的作用是产生UART工作所需的时钟信号,其频率定为实际波特率的16倍。波特率发生模块本质是1个可预置初值的计数器,每当计数达到预置值时输出高电平,其余值输出低电平。

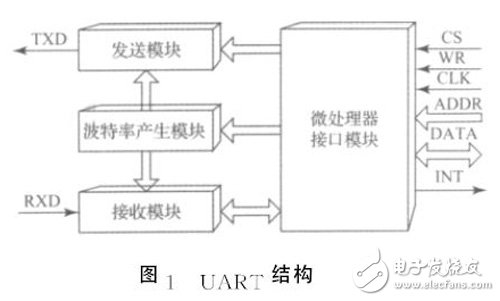

3.2 发送模块发送模块按照用户设置,将TxHolder中的并行数据串行发送出去,其核心为1个有限状态机,其状态转换如图2所示。

1)Idle状态

当系统上电复位之后,发送状态机即进入此状态。若不向发送缓冲器写入数据,那么TxDataValid为低电平,表示发送缓冲器空,状态机始终在此状态循环等待,TXD引脚输出高电平。

2)Start状态

一旦向发送缓冲器TxHolder 中写入数据,TxDataValid即变为高电平。状态机由Idle状态切换到Start状态,TXD输出低电平,输出起始位。

3)Shift状态

1位波特时间过后,状态机无条件的转换到Shift状态,即使能发送移位寄存器,开始将并行数据逐位右移,实现并串转换并输出到TXD。当输出的数据个数达到Databit设定的数据位宽时,便转换到Parity或者Stop_1bt状态,否则仍转换到该状态。

4)Parity状态

若数据位部分发送完毕,且奇偶校验使能位ParityEn=‘1’时,则转换到该状态。该状态下,根据已发送的数据和选择的校验模式,发送校验位。

5)Stop_1bit状态

无论停止位为1位还是2位,都先转换到Stop_1bit状态,先输出1位停止位。由该状态转换下一状态时,次态会有多种情况。若设置了stopbit为‘1’即选择2位停止位时,次态为stop_2bit;若stopbit为‘0’且发送缓冲器为空时,次态即转换到idle状态,否则转换到start状态开始新一轮的数据发送。

6)Stop_2bit状态

若选择2位停止位时,才会进入此状态。持续1个波特时间后,根据TxDataValid状态,进入Idle状态待命,或进入Start状态开始新1轮的数据发送。

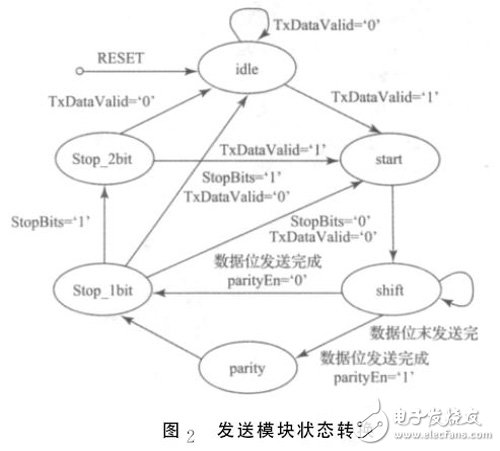

发送模块的行为仿真时序图如图3所示。其UART参数设置为偶校验、8位数据位和1位停止位。txclk为发送采样时钟信号,在该信号的上升沿,发送状态机状态翻转,同时数据被送到TxOut(TXD)引脚。图中TxOut输出的数据为“00100110011”,去掉起始位、校验位和停止位后即为待发送的数据0x32。由仿真所得发送模块的时序图可知,该模块各信号仿真结果正确无误。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)