QuickPlay 的高级工作流程让软件开发人员迅速构建基于 FPGA 的高效应用。

FPGA 实现相当复杂,这也是阻碍其广泛采用的主要障碍。到目前为止,在基于 FPGA 的平台上开发应用的唯一途径仍是采用一些最底层的硬件实现方案。这不仅让软件开发人员这一庞大的潜在客户群无法使用 FPGA 器件,还让传统 FPGA 设计人员的日子越来越不好过。

近期涌现的 FPGA 设计方法以高层次综合(HLS)工具为中心,充分利用 OpenC++L ™、C 和C++ 等软件编程语言的优势,为软件开发人员提供了沙盒效应,在大量应用中能从基于 FPGA 的硬件加速中大受裨益。但这些方法往往存在一个关键的不足,即无法让软件开发人员定义并配置最适合其应用的硬件基础架构。业界一直都在追寻高级工作流程的圣杯,从而无需 FPGA 专业技术即可在基于FPGA 的平台上实现应用。

PLDA 在过去五年中已经开发出一种这样的工作流程。称作 QuickPlay 的工作流程能够高效解决实现复杂性问题,为 FPGA 开发提供多种使用模式。但其价值的核心源头之一是它让软件开发人员将原本用于 CPU 的应用部分或全部地实现在 FPGA硬件上的方式。QuickPlay 能够全面发挥 FPGA 资源的作用,将这些功能强大而复杂的器件转化为软件定义平台,无需艰苦的硬件设计即能获得 FPGA 带来的优势。

试想一种可以细分为两项功能的软件算法: 其中一项功能用于数据处理,然后另一项功能用于数据的进一步处理。从软件角度看,这种实现方案相当简单,就是先调用 FuncTIon1(),接着再单独调用FuncTIon2(),使用指针来定位待处理数据的位置。

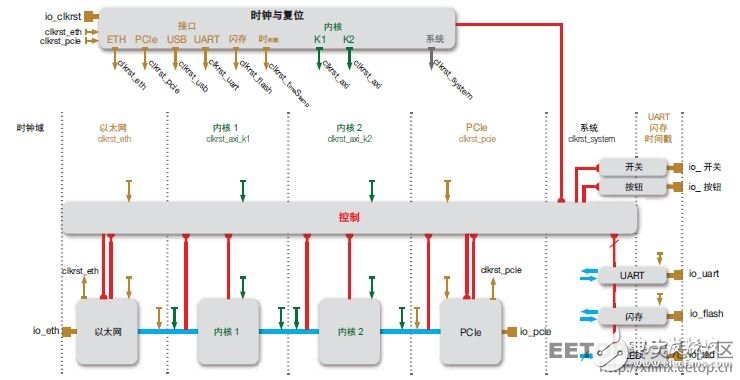

如果没有合适的硬件抽象工具流程辅助,在基于 FPGA 的硬件平台上实现这种算法需要软件开发人员处理图 1 所示的硬件设计(其中内核 1 和内核2 分别是 FuncTIon 1 和 FuncTIon 2 的硬件实现)。该硬件设计需要包含两个元素:控制层面和数据层面。

控制层面起着执行引擎的作用,用于生成时钟与复位、管理系统启动、编排数据层面运行以及执行所有维护功能。数据层面例化并连接处理元件元、内核 1 和内核 2 以及用于读入数据和写出处理后数据所需的必备 I/O 接口。虽然不同的应用会要求使用不同的 I/O 接口,不过在我们的实例中使用的是以太网和 PCI Express(PCIe)这些接口,如图1 所示。

图 1 — 使用传统 FPGA 工具实现两功能算法的详细硬件实现

无需硬件专业知识,软件开发人员使用编译软件功能 Function1() 和Function2()(一般用 C 或 C++语言编写)的 HLS 工具就可以轻松地生成内核 1 和内核 2 到采用 VHDL 或 Verilog 等的 FPGA 硬件描述中。但是设计中每一个从性质上不属于算法的其他元素(接口、控制、时钟及复位)都不能用 HLS工具生成,硬件设计人员必须将它们设计为自定义硬件描述语言功能或 IP。获得这些元素并将它们连接起来构成了另一个难题,因为部分元素可能并非是现成的,或是具有不同的接口(类型和大小)、时钟要求以及专门的启动顺序等。

QuickPlay 能够充分利用 FPGA 资源,将这些功能强大而复杂的器件转化为软件定义平台,无需艰苦的硬件设计即能获得由FPGA 带来的优势。

除了设计工作,同样具有难度的是实现工作。这包括将设计映射到选定 FPGA 平台上的资源、生成适当的约束以及确认在 FPGA 硬件上完成逻辑综合与实现后满足这些约束要求。在新的 FPGA 硬件上实现有效设计也需要耗费一名经验丰富的硬件设计人员数星期的时间。

因此,任何旨在使用自定义硬件帮助软件开发人员来增强其应用的工具必须能够:

• 从纯软件代码中创建功能硬件;

• 根据需要采用现有的硬件 IP 模块;

• 调用并创建所有的支持硬件(接口、控制、时钟等);

• 支持使用现成商用开发板以及自定义平台;

• 确保生成的硬件能自动建构校正,这样无需进硬件调试;且

• 支持仅使用标准软件调试工具即可调试功能模块。

PLDA 重新设计 QuickPlay 以满足所有各项要求,让纯软件开发人员以极小工作量就能指定、构建和集成 FPGA 到自己的软件架构中。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)