目前,多微机系统在许多方面得到了应用,诸如工业机器人控制、数控机床控制等。于是,多机之间的通信便成为多机系统的技术关键。特别是对数据传送有特殊要求的场合,更要解决好多机间的通信问题。如在工业机器人的控制中,对数据的传送就有如下要求:①主、从机要共享许多数据;②主、从机需要快速交换信息。在这种特殊要求下,传统的串行、并行通信就难以满足要求,而采用多机共享RAM电路,既能满足要求,又具有简单、可靠、通用性好等优点。

电路原理

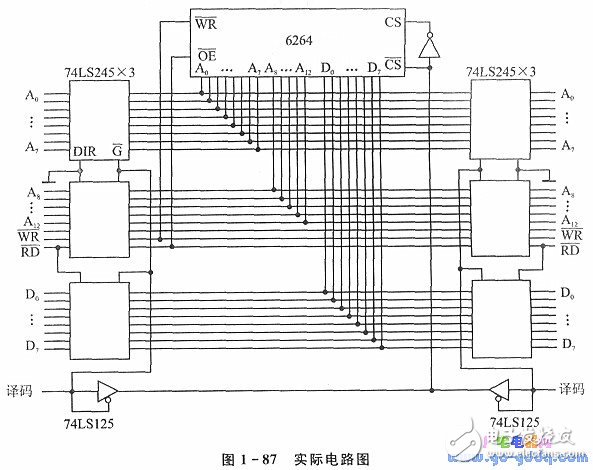

图1- 87所示为实际电路图。图中共用的RAM为6264.它有8根数据总线(Do~D7),13根地址总线( Ao~A12),4根控制总线(WR、OE、CS、CS),2根电源线。当两微机系统共用RAM时,必须用缓冲器将其隔离。当某机需要占用时,则对一机导通,而对另一机隔离;否则两机将同时出现故障。在图1- 87所示电路中,缓冲器选用74LS245,它是8位双向缓冲器。因为6264共有24根总线,故用6片74LS245与一片74LS125三态门。74LS245有一个方向控制端DIR,一个允许端G。DIR直接接于RD或接固定电位(+5 V,0 V)。用于数据线缓冲时,DIR要接RD;用于地址线和控制线时,DIR要接固定电位(+5 V,0 V)。一般的CPU,RD信号总是出现在地址信号的后面,如8080、8031等。如果G接于RD,则会出现RAM数据还没准备就写或读,系统就会出现故障。因此,G接于系统的译码端是比较合适的。

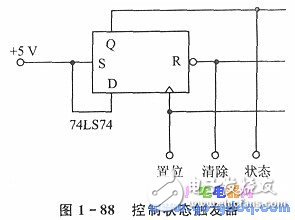

系统共用RAM,用缓冲器隔开,还有问题:如果两机同时使用RAM,则会发生冲突,双机都发生故障。解决的办法是,另外设置一个状态触发器,如图1- 88所示。采用74LS74中的一个D型触发器,当一机准备使用共用RAM时,先测试触发器的输出端Q,如果Q=O,则表示RAM状态为闲;然后,微机发出一置Q=1命令,表示RAM已采用;用完后,微机发出Q=O命令,使RAM为闲,其他微机可以采用了。

共用RAM的地址,在不同的系统中有所不同。这取决于译码的地址,即同一存储单元对于不同的系统有不同的地址。

从以上分析可知,此种多机共用RAM电路在两机有大块数据交换时,只需对各自RAM使用查询、置状态、清状态三个过程,故对于大块数据交换,传输速率要比传统的串行、并行高许多。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)