视频图像采集处理系统广泛应用于工业控制、工业检测、医学、机器视觉等领域,并且视频通信是3G时代多媒体应用的重要部分,日常生活中所见到的数码相机、可视电话、电话会议等产品,实时图像采集是其最核心的技术。图像采集的速度与质量直接影响产品的整体效果。大多数嵌入式图像采集系统都是基于DSP、ARM技术,一些系统比较复杂、成本高、实时图像处理比较困难。本文所设计的基于STM32F417的图像采集系统具有采集图像质量无损、实时性好、功耗低、成本低等优势,适合在对信息采集的实时性和图像质量方面有较高要求的系统中应用。

1 系统硬件平台图像采集系统主要由STM32F417微处理器、CMOS摄像头、帧缓存器、SD卡、LCD液晶屏及其他外设组成。图像采集系统整体框图如图1所示。

1.1 核心微控制器

嵌入式微处理器以其高性能、低功耗等优势成为便携式系统的最佳选择。ST公司开发的STM32F417是基于ARM Cortex-M4内核的32位闪存微控制器。其主频为168 MHz,在此工作频率下其处理性能可达210 MIPS,且电流消耗仅为38.6 mA;支持多种低功耗工作模式;内部集成DSP和FPU指令,具备高性能的信号处理和浮点运算能力;同时带一个8~14位并行照相机接口。此外,STM32F417片上集成1 MB的Flash和196 KB的SRAM。采用STM32F417作为图像采集系统的控制核心,将大大提高系统的性能,降低功耗和成本。

1.2 CMOS摄像头

CMOS摄像头选用OmniVision公司的OV7670。其内嵌一个10位A/D转换器,可输出8位RGB/YCbCr/YUV格式的图像数据,最高帧频可达30帧/s,最大图像分辨率为640×480,供电电压为3.3 V。O7670带有标准SCCB总线接口,并兼容I2C总线接口。

1.3 帧缓存器

选用美国AverlogIC Technologies公司的大容量AL422B作为采样处理的共享数据RAM。它是一款存储容量为384 K×8 B的FIFO存储芯片,工作频率可达50 MHz。所有的寻址、刷新等 *** 作都由集成在芯片内部的控制系统完成。在本设计中,1帧图像数据包含320×240个像素,完整存储一帧图像需要153 600字节,AL422B所具有的容量完全符合系统的设计要求。

1.4 SD卡

SD卡是一种基于半导体快闪存储器的新一代记忆设备,有着广泛的应用领域。本设计选用金士顿8 G的SD存储卡存储采集信息,方便系统对信息的进一步处理。

1.5 LCD液晶屏及其他外设

LCD液晶屏选用3.2寸TFT液晶屏320QVT,分辨率为240×320,其数据引脚直接与FSMC总线接口相连。其他外设包括LCD接口电路、ZigBe e无线模块、JTAG调试电路、复位电路、晶振电路等。

1.6 图像采集电路的设计

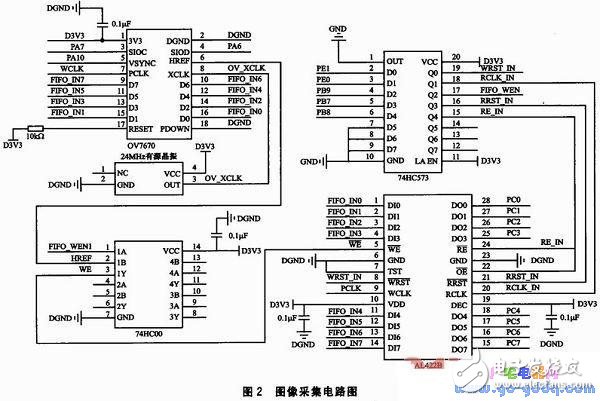

摄像头图像采集电路采用24 MHz有源晶振为OV7670提供系统时钟。为了解决微处理器与摄像头间的数据传输速率不一致问题,在二者之间加入一片AL422B帧缓存器,将摄像头采集的图像数据缓存后再送给微处理器。为实现将OV7670输出的图像信号自动地存入AL422B芯片,电路采用了一片与非门芯片74HC00,以便产生符合AL422B要求的写时序。需要注意的是,由于AL422B芯片正常工作需要3.3 V供电,如果STM32 F417使用3 V电压供电时,需要在两芯片接口之间增加一个74HC573 D锁存器,以满足高/低电平的要求。图像采集电路图如图2所示。

图像采集模块与STM32F417的接口电路示意图如图3所示。

在图3中,利用STM32F417的PC0~PC7口接收OV7670输出经过AL422B缓存后的8位图像数据。OV7670的SIO_D、SIO_C接口与STM32F417的PA6、PA7引脚相连,通过该接口实现对摄像头的初始化配置。STM32F417的PE0、PE1、PB7、PB8分别控制AL422B的时钟信号、写复位、读复位以及读使能信号。PB9与OV7670输出的行扫描信号通过与非芯片实现对帧缓存器写使能的控制,STM32F417的PA10引脚通过中断的方式检测摄像头是否输出一帧完整的图像。

由于OV7670带有标准SCCB接口,同时兼容I2C总线接口,本设计采用STM32F417产生的I2C总线信号模拟SCCB,实现对摄像头内部寄存器的初始化配置以及对其行场同步信号、开窗及输出格式的设置。对OV7670寄存器的配置方法如下:首先,发送OV7670的写地址0x42,然后发送写数据的目的寄存器地址和数据,从而初始化写 *** 作;通过发送OV7670的读地址0x43,完成对读 *** 作的初始化,从而实现对OV7670摄像头的初始化配置。

在对摄像头工作参数配置过程中,将OV7670的寄存器DBLV设为0x80,对输入时钟倍频数进行控制。设置寄存器BRIGHT、CONTRAS,控制图像的亮度和对比度。通过寄存器REG75、REG76设置图像边缘增强上、下限。在对摄像头测试阶段,首先将寄存器ACALING_YSC设为0x85,显示8色彩条,测试阶段结束后将该寄存器设为0x00,进入非测试模式。

OV7670输出同步信号包括:场同步信号VSYNC、行同步信号HREF、像素时钟PCLK。根据OV7670数据手册提供的同步信号时序图可知,OV76 70摄像头的像素时钟PCLK与FIFO写时钟WCLK相连接,在PCLK有效时将数据写入FIFO。场同步信号VSYNC为扫描一帧图像定时,在两个正脉冲之间完成一帧图像的扫描。

当STM32F417第一次检测到VSYNC下降沿时,系统第一次产生中断,表明OV7670开始输出一帧图像,STM32F417将FIFO_WEN置高电平,当HREF有效(高电平)时,FIFO_WEN与HREF通过与非门使能FIFO的WCK,将有效图像数据自动写入FIFO中。

当第二次VSYNC中断产生时,表明已经将一帧完整的图像写入FIFO,系统通过将FIFO_WEN置低,锁存一帧图像数据,实现图像的静态存储。此时,STM32F417送给FIFO的读时钟RCLK一个上升沿,将数据从FIFO中读出来,完成图像数据的实时采集与提取。

1.7 存储模块

SD卡支持SPI和SD两种模式,本设计采用SPI模式,将SD卡的CMD引脚与SFM32F417的SPI3_MOSI相连,CLK连接STM32F417的SPI3_SCK引脚,DATA0连接STM32F417的SPI3_MISO引脚,DATA3作为片选CS与STM32F417的PA15相连;在SD卡收到复位命令时,若CS为有效电平则启动SPI模式,SD卡在SPI3_SCK的控制下通过DATA0完成数据的读写。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)