在电子行业的基础设施和制造等领域,函数发生器都是有效的通用仪器。它可以生成不同频率和幅度的大量信号,用来评估新电路的运行情况,代替时钟信号,对新产品进行制造测试,及用于许多其它用途。

自第一部正弦波发生器问世以来,函数发生器的设计已经发生了多次演进,在当前数字领域中,大多数新型函数发生器(如Agilent 33220A)正采用一种新技术,称为直接数字合成(DDS)。DDS在大部分 *** 作中使用数字电路,从而提供了数字 *** 作拥有的许多优势。由于信号只在合成的最后阶段转换到模拟域中,所以在多个方面降低了函数发生器的复杂度,提高了函数发生器的稳定性。

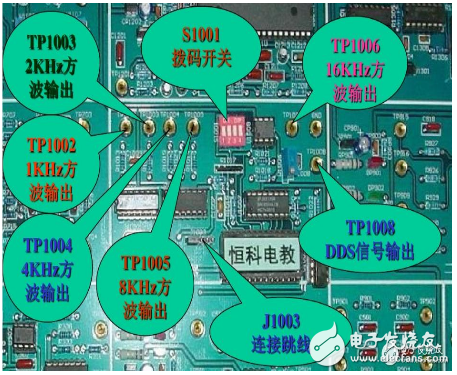

DDS函数信号发生器是什么----DDS信号发生器结构原理参考频率clock为整个合成器的工作频率,输入的频率字保存在频率寄存器0或1中,经32位相位累加后,再和相移寄存器累加以得到内部ROM的地址,然后经过内部ROM正弦波形表便可得到相应的幅度值,最后经过D/A转换和低通滤波器得到合成的正弦波。3.189C52和AD7008接口设计3.3正交信号形成电路设计

AD7008为单片DDS集成芯片,其结构如图所示。该器件内含32位相位累加器、正余弦查找表及10位DAC的DDS调制器,时钟频率可达20~50MHz;还内含两个10位乘法器、20位IQMOD寄存器及12位相位寄存器。除了可合成正弦波外,还可实现调频、调相、调幅及数字解调,同时提供了可与微机接口的并行和串行接口。

由于AD7008的相位累加器为32位,故2π=232,则△phase必须在0≤△phase≤232-1的范围内,每一时钟周期,32位累加器累加一个相位阶距,输出频率fout为:fout=△phasefclock/232

式中,fclock是参考频率。实际使用中,fout的上限取fclock的40%(考虑到相位噪声和杂散信号干扰)即△phase上限取0.4&mes;232。△phase可通过控制FSELECT从FREQ0、FREQ1中选择。尽管AD7008包含有32位相位累加器,但其输出仅为12位,因此没有必要也不可能用32位的分辨率。12位的相位数据经查询可转换成10位幅度信号。如果不要求调幅,IQ乘法器可以被旁路(CR2=0),而将正弦信号幅值直接送往DAC电路。通过外电阻Rset可对DAC满量程输出电流进行调节,公式如下:

Iout(mA)=6233Vref(V)/Rset(Ω)

DDS函数信号发生器是什么----DDS函数信号发生器优点DDS的主要优点之一是输出信号的频率精度可以达到作为发生器参考信号使用的晶体控制振荡器的水平。如果想实现更高的精度,也可以采用函数发生器本身的温度补偿晶体振荡器产生。这些信号可以提供高于0.1PPM的频率精度。在许多情况下,函数发生器还可以把频率锁定到外部实验室频率参考源上,从而生成超高精度的信号。

在许多实验室工作台上,另一部仪器如频率计数器可以提供最精确的恒温器控制的时钟振荡器,其输出参考信号可以作为DDS函数发生器的参考信号使用。在其它高精度测量实验室中,将通过在每个工作台上探测10MHz标准频率参考信号,以实现这一目的。根据数字电路的特点,DDS电路可以锁定在这一频率,从而提供与参考标准一样精确的信号。

DDS的第二个优点与第一个优点相关:DDS发生器可以生成非常高的频率精度。DDS信号发生器的数字电路可以实现与数字电路相同的频率精度。如果DDS电路有一个48位计数器,它可以提供高达48位的频率分辨率,而且日前,某些DDS合成器使用了位数更多及分辨率更高的计数器。

这种高分辨率意味着函数发生器能够准确地生成希望的输出频率,同时这还意味着发生器可以非常精确地改变频率。特别适合在通信、海量存储和类似应用中评估定时电路。目前能够生成几十MHz、分辨率为1mHz的DDS发生器并不少见。

由于所有的波形都是以数字方式生成的,因此函数发生器中的调制功能、扫描功能和突发生成功能都受到数字控制,并可以以非常高的精度进行设置。不仅可以精确地设置/改变频率和定时,还可以精确地设置/改变相位和幅度。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)