介绍了支持 JTAG标准 的IC芯片结构、 边界扫描 测试原理以及利用边界扫描技术控制IC芯片处于特定功能模式的方法。

针对IC芯片某种特定的功能模式给出了设计思路和方法,并用两块xc9572 pc84芯片互连的PCB板为例进行设计分析和实验实现。通过实验实现,体现了边界扫描技术易于电路系统调试和方便系统设计的特点,且设计的系统控制逻辑简单方便,易于实现。

当今,微电子技术已经进入超大规模集成电路(VLSI)时代。随着芯片电路的小型化及表面封装技术(SMT)和电路板组装技术的发展,使得传统测试技术面临着巨大的挑战。在这种情况下,为了提高电路和系统的可测试性,联合测试行动小组(JTAG)于1987年提出了一种新的电路板测试方法——边界扫描测试,并于1990年被IEEE接纳,形成了IEEE1149.1标准,也称为JTAG标准[1]。这种技术以全新的“虚拟探针”代替传统的“物理探针”来提高电路和系统的可测性。由于 JTAG标准的通用性很好, 现在许多IC公司都提供了支持边界扫描机制的IC芯片,甚至部分FPGA和CPLD芯片也采用了这一技术。

本文介绍支持JTAG标准的IC芯片结构,并以Xilinx公司的两块xc9572_ pc84芯片为例,探讨并利用边界扫描技术控制IC芯片处于某种特定功能模式的方法,并且针对IC芯片某种特定的功能模式设计该芯片的JTAG控制器。

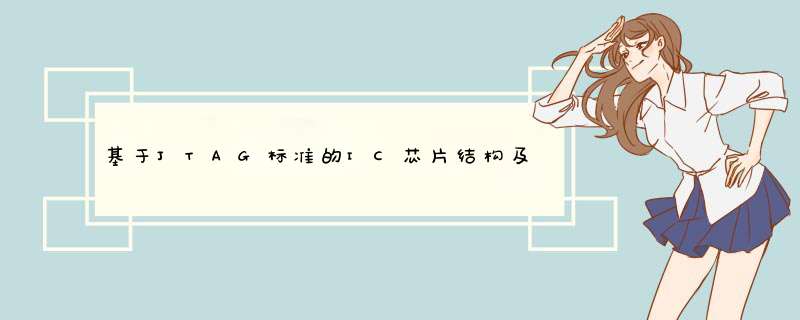

1 支持JTAG标准的IC芯片结构边界扫描技术的核心就是在IC芯片的输入输出引脚与内核电路之间设置边界扫描结构。JTAG 标准定义了一个4-wire串行总线[2],通过这四条测试线访问边界扫描单元,可以达到测试芯片内核与外围电路的目的。图1示出了支持JTAG标准的IC芯片结构。图中,扫描结构由测试存取通道(TAP)、边界扫描寄存器(BSR)、TAP控制器、指令寄存器(IR)和辅助寄存器等组成。

1.1 TAP

TAP是由4-wire串行测试线组成的测试存取通道,JTAG标准定义的所有 *** 作都由这四条测试线来控制。这四条测试线分别是:测试时钟输入线(TCK),测试方式选择输入线(TMS),测试数据输入线(TDI),测试数据输出线(TDO)。

1.2 TAP控制器

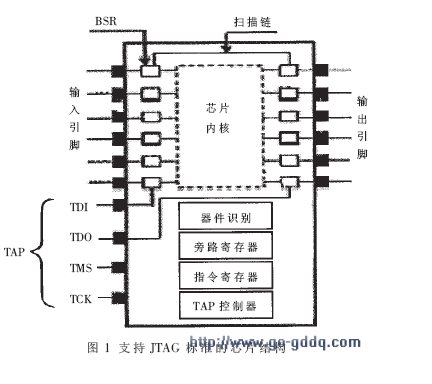

TAP控制器是边界扫描测试的核心控制器,具有一个16状态的有限状态机。它与TCK信号同步工作,并响应TMS信号。在TCK信号和TMS信号的控制下, TAP控制器可以选择使用指令寄存器扫描还是数据寄存器扫描,以及选择用于控制边界扫描测试的各个状态。图2描述了TAP控制器的状态转换全过程[3]。

无论当前状态如何, 只要TMS保持5个TCK 时钟为高电平, TAP控制器都会回到Test_Logic_Reset状态, 使测试电路不影响IC芯片本身的正常逻辑。需要测试时,TAP控制器跳出该状态, 选择数据寄存器扫描(Select_DR_SCAN)或选择指令寄存器扫描(Select_IR_Scan)进入图2的各个状态。一个标准的测试过程如下:TAP控制器在Capture_IR状态捕获指令信息, 经过Shift_IR状态移入新指令,新指令经过Update_IR状态成为当前指令;紧接着,当前指令在Select_DR_Scan状态选择相应的测试数据寄存器, 在Capture_DR状态捕获前一测试向量的响应向量,在Shift_DR状态移出该响应向量,同时移入下一测试向量,在Update_DR状态将新的测试量并行加载到相应的串行数据通道,直到移入最后一个测试向量为止。其中,Pause_DR状态和Pause_IR状态暂停数据移位状态;而四个Exit状态是不稳定状态,它们为状态转换提供灵活性。

1.3 BSR

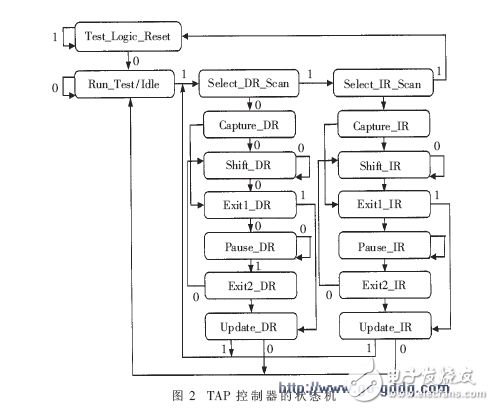

BSR是边界扫描技术的核心,它构成边界扫描链,其中的每一个边界扫描单元(BSC)都是由触发器Q、多路选择开关mux组成。图3示出了JTAP标准中BC_ 1 类型的BSC的结构[3]。

在图3中,SI为BSC的串行输入端,连接上一个器件(BSC)的串行输出端SO,依次相连便构成边界扫描链。该扫描链的首端接TDI引脚,末端接TDO引脚。当MODE为0时,芯片工作在正常模式下。当芯片工作在测试模式时,测试数据在移位信号(SHIFT=1)的控制下,通过SI 端进入到多路选择器1(MUX1)中,通过SO端进入下一个BSC的SI端;当芯片工作在捕获方式时(SHIFT=0),触发器Q1将捕获BSR并行输入端(DI)的数据,送入SO端,在扫描链中传递捕获的数据,并在TDO回收数据,以此来检测故障的存在并且定位故障所在的位置。当MODE为1时,芯片工作在更新方式下,Q1中的数据在更新信号(UPDATE)的作用下,进入到多路选择器2(MUX2)中,通过BSR的并行输出端(DO)进入芯片的内核中。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)