是指集成电路中至少有一个是有源元件的两个以上元件和部分或者全部互连线路的三维配置,或者为制造集成电路而准备的上述三维配置。通俗地说,它就是确定用以制造集成电路的电子元件在一个传导材料中的几何图形排列和连接的布局设计。

专利保护

集成电路布图设计实质上是一种图形设计,但它并非是工业品外观设计,不能适用专利法保护。因为,从专利法的保护对象来看,针对产品、方法或其改进所提出的新的技术方案要求具有创造性、新颖性和实用性。这一点对集成电路布图设计而言往往难以做到。从专利的的取得程序,专利申请审批的时间过长,成本较高,不利于技术的推广和应用。

集成电路布图设计虽然在形态上是一种图形设计,但它既不是一定思想的表达形式,也不具备艺术性,因而不在作品之列,不能采用著作权法加以保护。而且集成电路布图设计更新换代较快,若用著作权法来保护布图设计,则会因著作权的保护期过长而不利于集成电路业的发展。

由于现有专利法、著作权法对集成电路布图设计无法给予有效的保护,世界许多国家就通过单行立法,确认布图设计的专有权,即给予其他知识产权保护。美国是最先对布图设计进行立法保护的国家,随后,日本、瑞典、英国、德国等国也相继制订了自己的布图设计法。1989年5月,世界知识产权组织通过了《关于集成电路的知识产权条约》。此外,《知识产权协定》专节规定了集成电路布图设计问题,其缔约方按照上述公约的有关规定对布图设计提供保护。

我国的集成电路布图设计保护相对较晚。2001年3月28日国务院通过了《集成电路布图设计保护条例》,于2001年10月1日生效。根据《集成电路布图设计保护条例》,特制定《集成电路布图设计保护条例实施细则》,自2001年10月1日起施行。根据《中华人民共和国集成电路科设计保护条例》,制定《集成电路布图设计行政执法办法》,自2001年11月28日起实行。

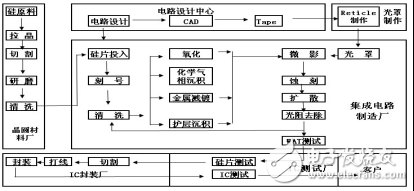

集成电路设计的流程图

集成电路设计的流程一般先要进行软硬件划分,将设计基本分为两部分:芯片硬件设计和软件协同设计。

芯片硬件设计包括:

1.功能设计阶段。

设计人员产品的应用场合,设定一些诸如功能、 *** 作速度、接口规格、环

境温度及消耗功率等规格,以做为将来电路设计时的依据。更可进一步规划软

件模块及硬件模块该如何划分,哪些功能该整合于SOC 内,哪些功能可以设

计在电路板上。

2. 设计描述和行为级验证

功能设计完成后,可以依据功能将SOC 划分为若干功能模块,并决定实现这些功能将要使用的IP 核。此阶段间接影响了SOC 内部的架构及各模块间互动的讯号,及未来产品的可靠性。决定模块之后,可以用VHDL 或Verilog 等硬件描述语言实现各模块的设计。接着,利用VHDL 或Verilog 的电路仿真器,对设计进行功能验证(funcTIonsimulaTIon,或行为验证 behavioral simulaTIon)。注意,这种功能仿真没有考虑电路实际的延迟,也无法获得精确的结果。

3.逻辑综合

确定设计描述正确后,可以使用逻辑综合工具(synthesizer)进行综合。

综合过程中,需要选择适当的逻辑器件库(logic cell library),作为合成逻辑

电路时的参考依据。

硬件语言设计描述文件的编写风格是决定综合工具执行效率的一个重要

因素。事实上,综合工具支持的HDL 语法均是有限的,一些过于抽象的语法

只适于作为系统评估时的仿真模型,而不能被综合工具接受。

逻辑综合得到门级网表。

4.门级验证(Gate-Level Netlist VerificaTIon)

门级功能验证是寄存器传输级验证。主要的工作是要确认经综合后的电路是否符合功能需求,该工作一般利用门电路级验证工具完成。注意,此阶段仿真需要考虑门电路的延迟。

5.布局和布线

布局指将设计好的功能模块合理地安排在芯片上,规划好它们的位置。布线则指完成各模块之间互连的连线。注意,各模块之间的连线通常比较长,因此,产生的延迟会严重影响SOC的性能,尤其在0.25 微米制程以上,这种现象更为显著。 目前,这一个行业仍然是中国的空缺,开设集成电路设计与集成系统专业的大学还比较少,其中师资较好的学校有 上海交通大学,哈尔滨工业大学,哈尔滨理工大学,东南大学,西安电子科技大学,电子科技大学,复旦大学,华东师范大学等。这个领域已经逐渐饱和,越来越有趋势走上当年软件行业的道路。

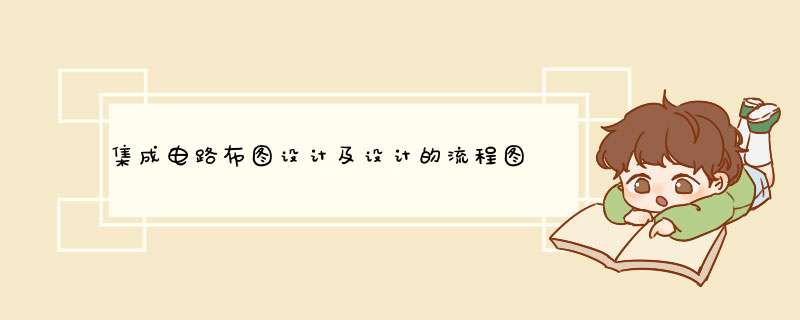

设计过程

1.电路设计

依据电路功能完成电路的设计。

2.前仿真

电路功能的仿真,包括功耗,电流,电压,温度,压摆幅,输入输出特性等参数的仿真。

3.版图设计(Layout)

依据所设计的电路画版图。一般使用Cadence软件。

4.后仿真

对所画的版图进行仿真,并与前仿真比较,若达不到要求需修改或重新设计版图。

5.后续处理

将版图文件生成GDSII文件交予Foundry流片。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)