纳米电子和数字技术研究与创新中心 Imec 在 2021 年国际电子器件会议(IEEE IEDM 2021)上展示了其最新研究成果。通过在基于 p 型氮化镓 (GaN) HEMT 的 200-V GaN-on-SOI smart 上共同集成高性能肖特基势垒二极管和耗尽型 (d-mode) 高电子迁移率晶体管 (HEMT)在 200 毫米基板上开发的功率集成电路 (IC) 平台,可以构建具有更多功能和性能的芯片。这将单片集成 GaN 功率 IC 提升到一个新的水平,并为更小、更高效的 DC/DC 和负载点转换器铺平了道路。

“d 模式 HEMT 通过用 DCFL [直接耦合 FET 逻辑] 替换 RTL [电阻器/晶体管逻辑] 的反相功能来改进逻辑/模拟功能,这改善了反相栅极的上拉特性,”说Imec GaN 技术项目总监 Stefaan Decoutere 在接受 EE TImes 采访时表示。“其背景是 GaN 中没有好的 p 沟道器件 [与电子相比,空穴的迁移率大约低 60 倍],因此像 CMOS 中的互补逻辑是不现实的。低压肖特基二极管提供额外的片上功能,例如电平转换和钳位。高压功率肖特基二极管可用于改善低边开关的第三象限运行[更好的电源效率]。”

根据 Decoutere 的说法,下一个目标是使这个扩展的 GaN IC 平台达到高度成熟度,并将其用于原型设计和工艺转移。在 200 毫米上开发它的好处是它更便宜。“虽然直到几年前 GaN-on-Si [硅基氮化镓] 是在更小直径的晶圆 [4 英寸和 6 英寸] 上加工的,但越来越多的晶圆厂已将其 GaN 技术转移到 200 毫米或将其安装在200 毫米晶圆厂,”Decoutere 说。

他补充说,大直径 GaN-on-Si 衬底面临的挑战是衬底的机械稳定性,因为 GaN/AlGaN 层的热膨胀系数与下面的衬底之间存在很大的不匹配。“但通过适当设计缓冲液,例如使用超晶格缓冲液和改进的 MOCVD 沉积工具,这种机械稳定性问题已经得到解决,使得在 200 毫米衬底上加工 GaN 成为可能。”

氮化镓 HEMT

GaN 是一种宽带隙 (WBG) 半导体,在许多以前由 Si 基元件主导的功率应用中获得了吸引力。高效率、在比硅更高的开关频率和温度下工作的能力以及微小的占位面积只是使这种 WBG 材料能够处理最苛刻的电源应用要求的几个特性。

近年来,GaN HEMT 因其广泛的应用而受到广泛关注,其中包括从高频功率放大器到电力电子系统中使用的高压器件的各种应用。该行业目前正专注于在硅基衬底上开发 GaN HEMT,以降低成本并将 GaN 与硅基组件集成。另一方面,直接开发 GaN-on-Si 面临缺陷密度高的问题,这会降低性能、可靠性和良率。由于 GaN 和 Si 之间的晶格和热失配,缺陷经常在 GaN/Si 异质界面处形成。

GaN HEMT 具有出色的 R DS(on)和品质因数值。FOM 可以比超级结场效应晶体管 (FET) 低 4 倍至 10 倍,具体取决于电压和电流额定值。因此,GaN 非常适合高频应用。当使用具有低 R DS(on)值的 GaN HEMT 时,传导损耗会降低,效率会提高。

GaN HEMT 中没有反向恢复电荷,因为它们缺少固有的体二极管。这些器件表现出取决于栅极电压的可变特性,并且固有地能够反向传导。由于不需要反并联二极管,因此反向传导能力在系统级优于典型 IGBT。通过消除反向恢复损耗,GaN 即使在高开关频率下也能实现高效运行。

驱动 GaN 比驱动 MOSFET 更困难,因为它需要更快的开启和关闭时间(这意味着更高的 dV/dt),以及更低且更严格控制的栅极开启电压。优化栅极环路电感、电源电感、栅极电阻以及漏极和源极电感是在 PCB 级驱动 GaN 的关键问题。设计人员应专注于栅极驱动器 IC 级的死区时间控制、dV/dt 抗扰性、负源电压和栅极过充电。栅极驱动器高端和低端之间的对称性是一个重要特性,因为它实现了小于 1ns 的延迟匹配,从而减少了死区时间。

IMEC的研究

目前,GaN 电力电子器件仍以由产生开关信号的外部驱动器 IC 驱动的分立元件为主。但是,有一种情况可以充分利用 GaN 提供的快速开关速度,从而还将驱动器功能集成到单片解决方案中。

由于缺乏具有可接受性能的 GaN p 沟道器件,提高 GaN 功率 IC 的全部性能的主要障碍之一仍然是寻找合适的解决方案。CMOS 技术使用对称的 p 型和 n 型 FET 对,基于两种 FET 的空穴和电子迁移率。然而,在 GaN 中,空穴的迁移率比电子的迁移率差大约 60 倍。这意味着间隙为主要载流子的 p 沟道器件将比其 n 沟道器件大 60 倍,而且效率极低。一种流行的替代方法是用 RTL 代替 P-MOS,但要在切换时间和功耗之间进行权衡(图 1 和图 2)。

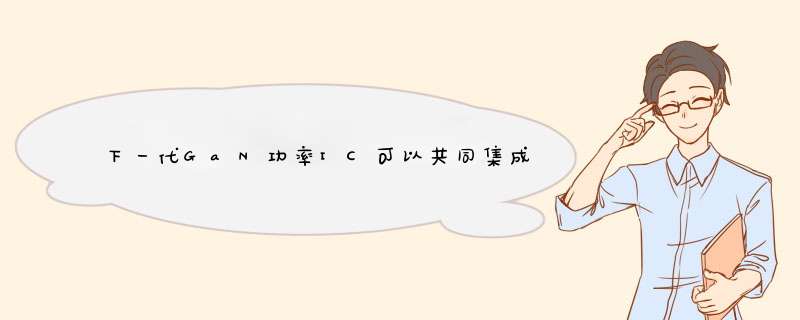

图 1:在 200 毫米 GaN-on-SOI 衬底上制造的高压元件的工艺横截面:(a) e 模式 pGaN-HEMT (b) d 模式 MIS HEMT,和 (c) 肖特基势垒二极管。 所有器件都包括基于前端和互连金属层并由介电层隔开的金属场板。

Imec 通过结合 e-mode 和 d-mode HEMT 器件提高了性能。根据 Decoutere 的说法,在 SOI 上扩展 e-mode HEMT 功能平台与共同集成的 d-mode HEMT 可以提高电路的速度并降低电路的功耗。

共同集成到 GaN 功率 IC 中的另一个关键组件是肖特基势垒二极管。肖特基 GaN 二极管比硅二极管具有更高的阻断电压和更低的开关损耗。它们的集成使 Imec 转向基于 GaN 的智能功率 IC。据 Imec 称,GaN IC 平台可通过我们的多项目晶圆服务进行原型设计,并准备好转让给合作伙伴。目标是开发和发布用于高压电源开关和转换应用的 650V 版本平台,以及用于手机、平板电脑和笔记本电脑的快速充电器。

审核编辑:郭婷

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)