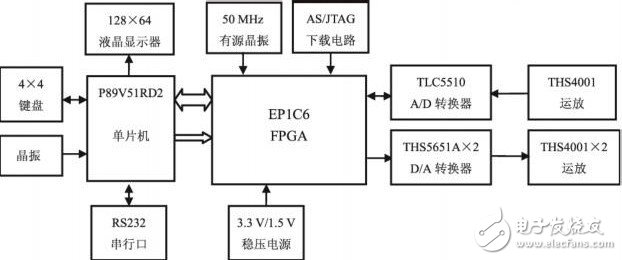

大学生电子竞赛题目以模拟电子、数字电子、可编程逻辑器件及单片机技术为核心, 涉及电子仪器仪表、通信、高频无线电、自动控制等多学科内容。2007 年电子设计竞赛组委会专家指出: 电子设计竞赛的发展趋势将以模电、数电、FP2GA 为重点。因此, 对于参赛队员来说要获得较好的成绩, 选择合适的题目并进行培训至关重要。笔者针对以FPGA 为核心的竞赛题目特点及竞赛元器件要求, 设计制作了竞赛电路板, 组成框图如图1 所示。

图1 电子竞赛电路板组成框图

本设计主要包括3 个部分: 单片机扩展电路、FPGA 核心电路、高速A/ D 和D/ A 转换电路。其中单片机扩展电路主要包括振荡电路、液晶显示模块接口、按键、复位电路等,这部分既可以进行基本的单片机实验, 还可以为FPGA 核心电路提供控制信号及利用FPGA 的资源等; FPGA 核心电路部分主要由电源、J TAG 下载、AS 下载、输入输出电路等组成; 高速A/ D 和D/ A 转换电路具有一路模拟信号输入、两路模拟信号输出。设计将3 部分有机地结合在一起, 组成了一个实验系统, 它既能够完成等精度频率计、DDS 信号发生器、数字示波器等竞赛题目的设计, 又可以用于赛前培训。

1 电路设计 1. 1 FPGA 核心电路板。 1. 1. 1 FPGA 芯片选择FPGA 是英文Field Programmable Gate Array 的缩写, 即现场可编程门阵列, 它是在PAL, GAL, EPLD 等可编程器件的基础上进一步发展的产物。它是作为专用集成电路( ASIC)领域中的一种半定制电路而出现的, 既解决了定制电路的不足, 又克服了原有可编程器件门电路数量有限的缺点。

经过分析近几届电子设计竞赛中的题目, 发现设计题目对FPGA 的功能要求不是太高, 一般常用的FPGA 都能满足设计要求。通过比较, 知道Alter a 公司的Cyclone 系列FPGA具有低成本的特点, 而且平衡了逻辑、存储器、锁相环和高级I/ O 接口。所以Cyclone 系列FPGA 是设计的最佳选择。

Altera 公司Cyclone 系列中的EP1C3, EP1C6, EP1C12完全能够满足设计题目要求, 所以可以从这几种芯片里选择FPGA.综合比较选择了EP1C6 系列的芯片, 这个系列中的EP1C6T 144C8 完全能够满足电子大赛的要求。而且EP1C6T 144C8 也支持SOPC ( System On Pr ogrammingChip) , 可以实现嵌入式的软CPU( 如NIOSII 等) , 为嵌入式电子设计提供了又一种选择。所以在此选择EP1C6T144C8作为此设计的FPGA 芯片。EP1C6T144C8 内部具有5 980个逻辑单元( LE) 、20 个M4K RAM 块、92 160 位嵌入式RAM、2 个锁相环、96 个I/ O 口, 支持AS、JTAG 下载, 采用TQFP144 封装形式。

1. 1. 2 FPGA 电路板设计EP1C6T144C8 是144 脚的FPGA 芯片, 引脚分类及功能如下:

( 1) 电源引脚。使用3. 3 V 电压作为供电电源, 可以为满足各种数据传输标准的输出缓存器的提供电源, 也可以为满足LVT TL, LVCMOS, 各种PCI 接口标准的输入缓存器提供电源。

( 2) 内部逻辑门的电源引脚。使用11 5 V 电压作为供电电源, 可以为满足LVDS, SSTL2, SST L3 接口标准的输入缓存器提供电源。

( 3) 锁相环的电源引脚。锁相环的电源无论是否使用,必须将此引脚连接到11 5 V 供电电源。

( 4) 配置引脚。包括为JTAG 边界扫描测试配置接口和AS 主动串行配置接口。

( 5) 用户I/ O 口引脚。FPGA 芯片的用户I/ O 引脚为96个, 通过双排插座引出。这些接口分为3 类: 与单片机的接口、扩展接口、与A/ D 转换器及D/ A 转换器的接口。

( 6) 时钟引脚。采用50 MH z 有源晶振, 输出时钟信号经低阻值电阻缓冲后接CLK0, 即FPGA 的管脚16.

1. 2 单片机扩展接口电路设计 1. 2. 1 单片机80C51 系列单片机作为8 位单片机事实上的工业标准,世界上众多电气公司都生产其系列产品, 有广泛的选择及应用基础。如ATMEL 公司的AT 89C5X, AT89S5X, NXP 公司的P89C5X, P89V5X 等。本设计选择了NXP 公司的P89V51RD2 单片机, 该单片机片内具有64 K 字节的可反复擦写的可在线下载编程的( ISP) FLASH 程序存储器和256字节的RAM、1 K 字节的扩展RAM、32 个I/ O 口、3 个可编程定时计数器、一个串行口、一个SPI 接口等功能。

1. 2. 2 液晶显示模块采用128@64 具有中文汉字库的图形点阵液晶显示模块, 内含8 192 个16@16 点中文字型和128 个16@8 半宽的字母符号字型; 另外绘图显示画面提供一个64@256 点的绘图区域GDRAM; 而且内含CGRAM 提供4 组软件可编程的16@16 点阵造字功能。电源 *** 作范围宽( 21 7 V to 51 5 V) ,低功耗设计可满足产品的省电要求; 同时与单片机等微控器的接口界面灵活( 3 种模式: 并行8 位/ 4 位, 串行3 线/ 2 线) 。

中文液晶显示模块可实现汉字、ASCII 码、点阵图形的同屏显示, 广泛用于各种仪器仪表、家用电器和信息产品上,并作为显示器件。中文液晶显示模块具有上/ 下/ 左/ 右移动当前显示屏幕及清除屏幕的命令, 具有光标显示/ 闪烁控制命令及关闭显示命令。预留多种控制线( 复位/ 串并选择/ 亮度调整) 供用户灵活使用。

1. 2. 3 键盘扩充16 个按键组成4@4 矩阵形式与单片机的P1 口相连。

1. 2. 4 与FPGA 接口单片机的P0 口, P2 口, RD, WR, ALE 分别经100 8 电阻与FPGA 预留I/ O 口相连。

1. 2. 5 RS232 接口扩充MAX232 串口芯片, 扩展串行口, 可以实现单片机与PC 机的串行通信、在线下载程序。

1. 3 高速模数转换器和数模转换器电路 1. 3. 1 高速模数转换器由于FPGA 为高速器件, 为实现速度匹配, 本设计采用高速A/ D 转换器TLC5510.它是由美国T I 公司生产的新型模数转换器件( ADC) , 是一种采用CMOS 工艺制造的8位高阻抗并行A/ D 转换芯片, 能提供的最高采样率为20MSPS.由于TLC5510 采用了半闪速结构及CMOS 工艺, 因而大大减少了器件中比较器的数量, 而且在高速转换的同时能够保持较低的功耗。在推荐工作条件下, T LC5510 的功耗仅为130 mW.由于TLC5510 不仅具有高速的A/ D 转换功能, 而且还带有内部采样保持电路, 从而大大简化了外围电路的设计。同时, 由于其内部带有标准分压电阻, 因而可以从+ 5 V 的电源获得2 V 满刻度的基准电压。TLC5510 可应用于数字T V、医学图像、视频会议、高速数据转换以及QAM 解调器等方面。T LC5510为24 引脚、SO、PSOP 表贴封装形式。

1. 3. 2 高速数模转换器高速D/ A 转换器选用了TI 公司生产的TH S5651A, 该芯片是经特别优化的用于有线和无线数据传输的10 位数模转换器。该芯片的制造采用了先进的高速混合信号CMOS工艺, 转换速率达125 MSPS.片上具有11 2 V 参考电压、D/ A转换输出为电流型, 电流范围为2 mA- 20 mA.功耗是5 V 工作时为175 mW, 工作在SLEEP 模式时为25 mW、封装为282引脚SOIC或TSSOP 封装。

1. 3. 3 高速运算放大器为了与高速A/ D、D/ A 转换器速度相匹配, 电路设计中还使用了美国TI 公司生产的TH S4001 高速电压负反馈运算放大器。其带宽可达270 MHz、转换速率达400 V/Ls, 能很好地实现系统的放大缓冲功能, 以满足系统性能指标要求。

2 结语本设计的电子竞赛电路板采用了MCU + FPGA 结构,单片机负责数据处理、控制显示等工作; FPGA 负责高速数据采集、数模转换工作。同时, FPGA 还可以为单片机提供存储器及I/ O 口等资源。在PCB 设计时, 特别要注意采取抗干扰措施, 如在电路中要适当配置去藕电容、数字地与模拟地分离, 最后在一点接于电源地等。本设计在地线的设计方面, 使用了屏蔽地、数字地和模拟地, 它们分别与电源地相连, 做到了数字电流不流经模拟器件, 高速电流不流经低速器件。本文涉及的电路通过调试, 各个模块可以达到预期的功能, 该电路板可以用于电子设计竞赛和一些电子产品的开发。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)