在当今这一代,电力电子设备几乎在从交流适配器到传输系统的各个领域都有应用。这些器件包含硅 (Si) 作为低压和高压器件的主要元素。然而,随着半导体行业的最新进展,碳化硅 (SiC) 已被证明是硅基 MOSFET 的继任者,因为它具有高电压阻断和高开关频率等宽禁带特性。

对于功率器件,可靠性和稳健性是高压应用需要考虑的关键因素。因此,对于SiC MOSFET,在广泛用于高压应用之前,需要进行适当的研究和评估。

电压 (Vth) 不稳定性

电压不稳定是由于电子电路的电力系统未能维持所有母线的电压水平,进而导致无功功率供需失衡

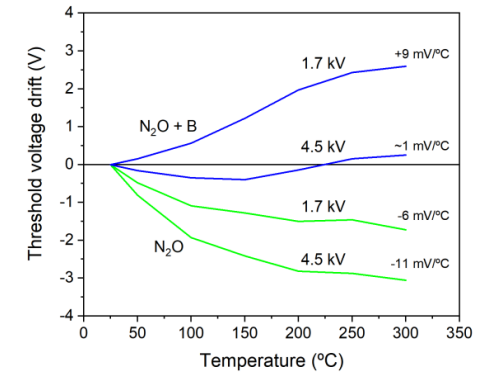

A. 温度不稳定性:在不同电压等级的器件中,SiC MOSFET 的阈值电压温度升高范围从室温到 300°C,如图 1 所示。

图 1:正负温度变化的实验 Vth

正如观察到的,具有标准 N2O 氧化的系统显示负 ΔVth,而用硼处理的 MOSFET 显示正 ΔVth,因为阈值的偏移与 SiO2/SiC 界面的电荷相关。在这种情况下可能会发生两种可能性——导致电路导通电阻增加的正温度 Vth 系数和导致正常开启 *** 作的负温度 Vth 系数,从而增加栅极驱动器的复杂性。

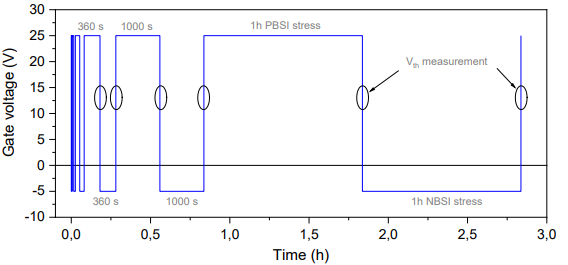

B. 偏置应力不稳定性:偏置应力不稳定性与 SiO2/Si 界面中存在的陷阱、电荷和缺陷有关,这些缺陷会导致 Vth 的差异。图 2 显示了专为 WBG 器件设计的栅极应力模式,其应力时间为 3 小时。这些测试是通过在 -5V 和 +25V 之间循环 MOSFET 栅极来完成的。

图 2:偏置应力不稳定性应力模式

如图所示,当漏极电压为 VDS = 0.1V 时,给出的最大正偏置应力为 +25V。Vth 值是从在从负偏压和正偏压转换期间测量的 IDS(VGS) 引脚获得的。

测试 SiC MOSFET 的可靠性

为了分析 SiC MOSFET 的稳健性,进行了各种可靠性测试。针对 SiC MOSFET 的各个关键区域考虑了设计和技术的可靠性。

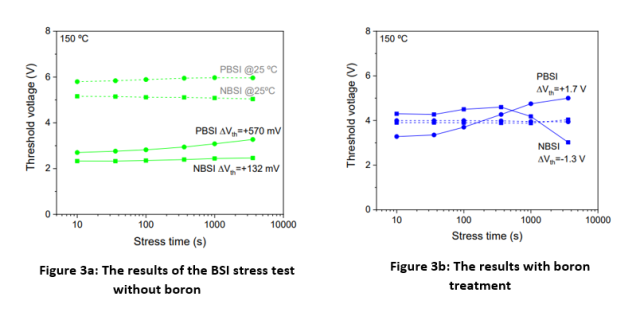

图 3:BSI 测试结果

图 3a 显示了 BSI 应力测试在 150°C 下对 4.5 kV 额定 25 mm2 阈值电压的结果,没有硼处理,图 3b 显示了硼处理的结果

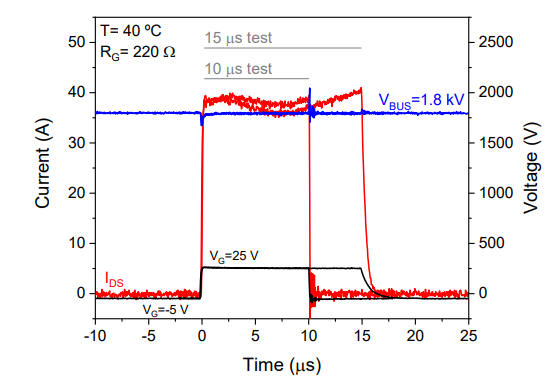

短路:如图 4 所示,短路行为已在电路处于阻塞模式 (VGS = -5V)、总线电压设置为 55%、栅极脉冲为 25V 时进行了分析。

图 4:短路测试

额定电压为 3.3kV 的 MOSFET 在室温下的波形如下图所示。

图 5:3.3kV 额定 MOSFET 的短路波形

短路故障的主要原因是输出能量施加的高内部温度升高。为了避免这个问题,使用较大的单元间距是有益的,因为它具有较低的通道密度和较大的散热面积。

功率循环:进行功率循环测试以进一步检查 SiC MOSFET 的稳健性,其中 10 万次 10ms 半正弦波循环施加到漏极。功率循环是根据 MOSFET 的自愈特性进行的,并且在大量恒流脉冲后耗散能量的演变中会吸收变化。针对栅极偏压的变化考虑了两种静止方案,以检查器件单位单元的受影响区域。

图 6:电源循环测试

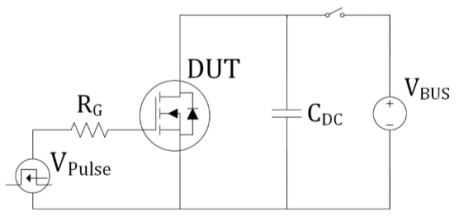

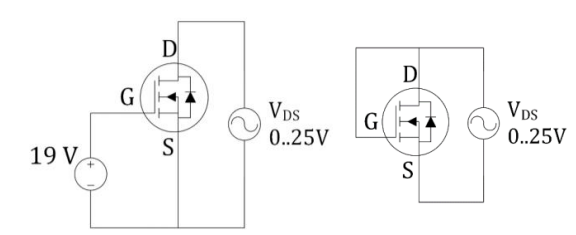

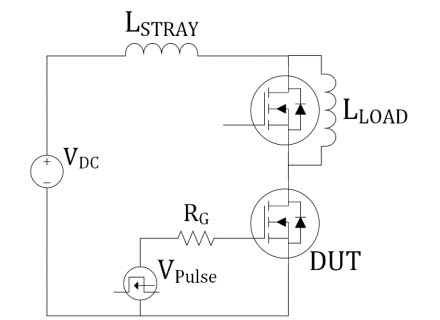

高温高压开关:使用双脉冲测试 (DPT) 开关电路,使用另一部分的内置体二极管测试 MOSFET 的动态性能,如图 7 所示。

图 7:DPT 开关电路

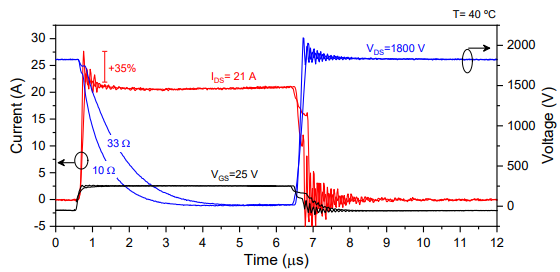

观察到制造的器件能够在具有显着大过冲的高总线电压下切换。图 9 显示了使用 RG 评估的开启和关闭特性。

图 8 额定电压为 3.3 kV 的 SiC MOSFET 的开关波形

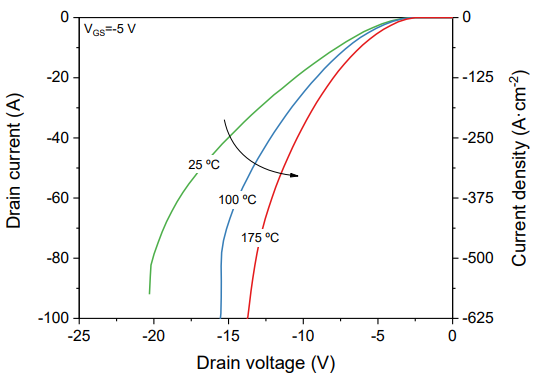

双极退化:平面 MOSFET 具有电流反向传导的特性,允许负漏极电压的电流流动。有一个内置的pin二极管,由p和n层组成,在应用过程中可以反并联导通。图 9 显示了 4.5kV MOSFET 的 IDS(VDS) 特性。观察到接近 SiC PN 内置电位的身体的膝点电压,同时观察到温度升高期间的电压变化。

图 9:IDS(VDS) 特性

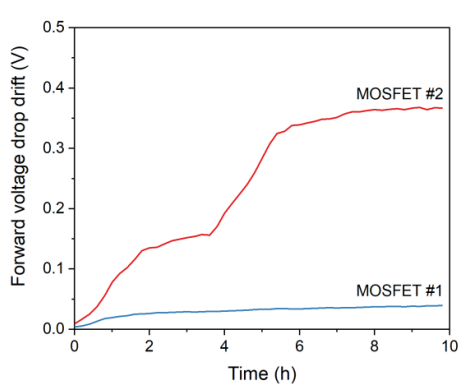

这些情况通常不会出现在纯 PiN 二极管中,也无法通过仿真重现。在多个 25mm2 3.3 kV MOSFET 的 PiN 二极管上进行进一步双极退化测试,以检查测试样品的可能退化。在这里,栅极偏压设置为 -6V,以确保电流仅流过 PiN。对于这个测试,20A·cm-2 的源电流密度持续 10 小时,同时监测 Vf。

图 10:10 h 20 A·cm-2 双极衰减测试

结果表明,两个测试器件的体二极管和正向压降 VF 均有所增加。器件 1 中的正向电压漂移也可以忽略不计,仅为 40 mV,而器件 2 的漂移更高,ΔVF=370 mV。这种电压漂移是不可逆的,它显示了由于存在堆垛层错而导致的 PiN 双极退化,这对 MOSFET 性能没有任何明显影响。

结论

MOSFET 在高压应用中的稳健性至关重要,因为它们在各种电力电子设备中发挥着重要作用。MOSFET 在用于任何设备或系统之前必须通过各种测试。Vth 漂移通过针对 WBG 设备的特定测试进行了测试。在浇口部分的存在对高于 100°C 的阈值稳定性有负面影响。在阈值偏移期间没有永久性损坏,并且在压力测试后 Vth 完全恢复。

最佳的单元电池设计将是短路时间和输出电流之间的最佳解决方案。还进行了 100 万次不影响输出性能的功率循环测试。制造的器件可以在高温下在高总线电压下切换,但在某些条件下存在显着的阈值漂移,导致其电气特性的退化,这是由它们的传输特性的变化引起的。这个问题后来归因于在导通状态和关断状态下栅极下方的内部自热的组合。这可以通过增加质量和散热片来改善,也可以通过在 MOSFET 中使用导热油脂来降低热阻,以获得更好的散热片。

上述结果提供了相当好的鲁棒性,因此有必要探索替代栅极堆叠形成以获得高性能和可靠的 SiC MOSFET。

审核编辑:汤梓红

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)