关于modelsim仿真时出现 No objects found matching ‘/*’ 问题在Modelsim6.2系列版本中仿真时,点击start simulateion后,出现Objects空白的问题,导致执行 add wave al l时出现“# (vish-4014) No objects found matching ‘/top_tb/*’。“的报错选项。尽管输入run后,可以运行仿真,但却无法察看wave窗口的波形。

这是优化的问题。

解决方法:1. 点击工具栏中的“simulate”按钮,调出start smulaTIon窗口,把窗口中最下边opTImizaTIon栏中的Enable opTImization项目前的钩钩去掉,然后选择仿真的文件,点击OK,就一切正常了,能看到objects了。

Quatus ii联合modelsim仿真无法产生波形或波形一直为Hiz状态原因分析

最近用用modelsim仿真Quatus写的testbench,遇到了波形无法产生的问题,一直卡在这里很久都没找到原因,经过一番分析和各种乱试,终于找到原因了。

在设置编译的test bench的时候,一定要把顶层模块设置为xx_vlg_tst(),就是启动test bench template writer的时候,软件给你自动产生的那个test bench的模块名。因为在仿真的时候,这个模块才是真正的顶层模块,是它实例化测试模块,并给与测试模块激励信号的。设置方法如下:

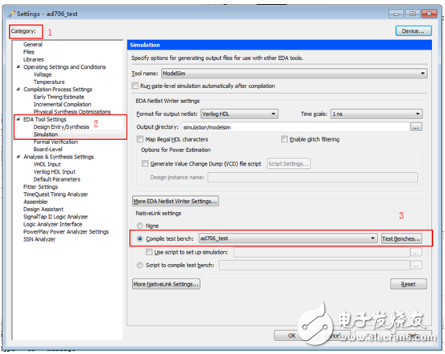

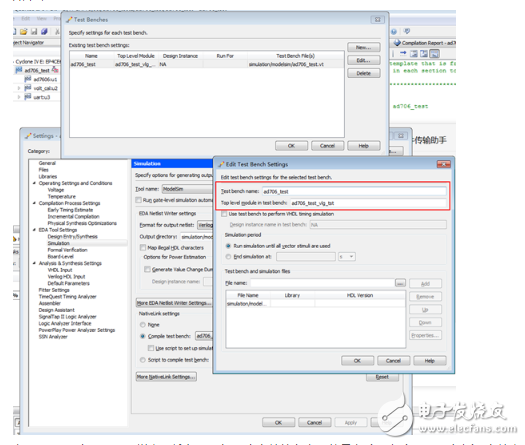

点击主界面菜单栏的Assignment——》Settings,出现Settings对话框,然后在Category栏选择EDA Tool Settings——》Simulation,出现以下界面,

点击3右边的Test Benches按键,出现Test Benches对话框,然后点击该对话框右边的New按键,出现了Edit Test Bench Settings对话框,如下,

在Test Bench name一栏中,输入test bench文件的名字,就是在simulation/modelsim文件夹中那个后缀为.vt的文件的名称,而Top level module in test bench一栏则要输入test bench文件中那个模块的名称,这个是自动产生的,名字都是xx_vlg_tst,xx为test bench文件的名称,记住,这里一定要设置好顶层模块是xx_vlg_tst,因为默认情况下它是和test bench name是一样的,如果这样设置,是无法产生波形的。

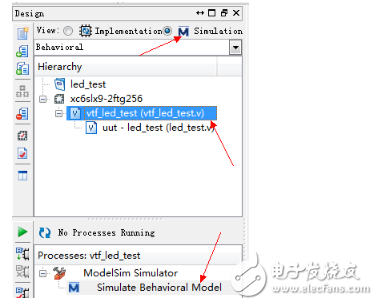

之前一直用ise联合modelsim仿真,ise里面就没有这些繁琐的步骤,在写test bench的时候,软件自动把test bench设置为了顶层模块,如图:

仿真的时候只需要点击vtf_xx.v文件,然后双击Simulate Behavioral Model就会调用modelsim,仿真test bench文件了。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)