成功的路上充满挑战,特别是在测试测量与医学成像应用领域尤其如此。上述领域涉及高精尖技术,因此要求采用速度最快、分辨率最高的电子技术,才能设计出独树一帜的未来产品。数字电子技术的发展正在推动相关领域的进步,而模拟电子技术也同样重要。

在测试测量与医学成像应用领域,数字电子技术通常在软件和/或固件控制下执行多种复杂功能。

现实世界的信号(如声和光等)是持续的,我们需采用模拟信号处理技术来应对" 真实"的环境。用模拟电子技术通过感应器进行信号采样并带动传感器。

我们可将数模转换器 (DAC) 与模数转换器 (ADC) 等混合信号产品用于实现模拟和数字之间的连接。尽管这些器件搭建了数字与模拟间的桥梁,但我们仍将其视为模拟元件。

本文将给出测试测量与医学成像应用领域的实例,并讨论未来的发展趋势。

医学成像:超声

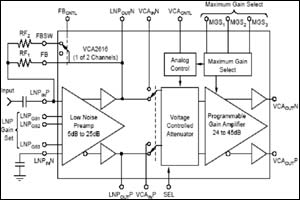

图 1 给出了超声通道的结构图。通常来说,接收机与发送器共用同一变送器。发送器将向变送器发送高振幅脉冲。这时将开关设置为接收机输入,以便检测回声或从病人处反 回信号。

我们提供钳位,以确保接收通道不因发送器的高幅度信号而饱和。低噪声放大器(LNA) 用于放大返回信号,并设置接收机的噪声系数。

随着信号深入人体组织,它会逐渐减弱,而返回信号则随着时间的流逝而要求更高的增益,以保持可接受的 ADC 水平。因此,LNA 随后还要加上时间增益放大器,该放大器编程后可补偿信号的衰减。

信号的带宽受低通滤波器 (LPF) 限制,能够降低通道内噪声,并达到防止信号混淆的目的。由于大多数高速的高精度 ADC 都使用差分输入,因此需将信号从单端 (SE) 转换为差分(Diff)。信号随后转换为数字形式,在数字域进行进一步处理。

在超声中形成的波束使用多个通道来构成图像。高性能系统中使用的通道超过 128个。新一代系统的通道数量还将继续增加,达到 1024 个。

图1 超声接收机结构图

超声的未来趋势

为了降低超声设备的成本并提高性能,我们应当对其功能进行集成。通常集成的第一步就是将多种部件集成在一个封装中,并借助先进的架构进行性能提升。因此,多通道系统不是用单个部件就可以实现的,而是通过多种部件的集成来实现,它们可使尺寸更小、功耗及成本更低、可靠性更高。

以TI的VCA2611/6(图2)与ADS5271(图3)为例,将多个放大器与 ADC 封装在一起。这些元件可用于实施以上所示大多数模拟信号的调节工作。

VCA2611/6 包含两个低噪声前置放大器 (LNP) 以及低噪声可变增益放大器 (VGA)。VCA2611 是 VCA2616 的升级版本,其输入处可处理 -2.0V 负向输入峰值,在低噪声前置放大器之前实现较慢的廉价输入钳位二极管 (VCA2616 只能处理 -0.3V 的峰值)。在某些设计中,我们甚至不需要输入钳位。

VCA2611/6 集成了有源终端 (AT) 作为其架构的一部分。通过有源终端可实现低输入阻抗,与传统的分路终端 (shunt terminaTIon) 相比,改善了 4.6dB 的噪声指数。我们也可改变终结值以适应不同的信号源。有源终端结合最大增益选择 (MGS) 可为我们实现最佳的噪声性能。

低噪声前置放大器具备差分输入与输出功能,可设置实现 5dB、17dB、22dB 或25dB 的增益。低噪声前置放大器的输出可用于外部信号处理,如低通滤波。

可变增益通过模拟电压进行控制,其增益可在 0dB 到最大增益选择寄存器设置的增益值之间变动。用户能够对可变增益进行编程,使动态范围最优化。VCA 输入可从低噪声前置放大器转换到外接电路,以适应不同的应用。将低噪声、增益以及增益范围的可编程性相结合,能够使 VCA2611/6 在许多应用中都成为一种功能丰富的构建块,因为对于这些应用来说噪声特性至关重要。

未来的 VCA2611/6 系列产品将实现更高的性能与功能,从而推动所用元件数量的减少。

图2 VCA2611/6 功能结构图(二选一通道)

ADS5271 是一款高性能、12 位、50MSPS 的 8 通道并行模数转换器 (ADC)。ADS5271 在 20MHz 上具备 70.5dBFS(典型)的 SNR 以及 82dBc(典型)的SFDR。

3.3V CMOS 技术实现了非常低的功耗,仅为 957mW,这为实现最高的系统集成密度留有余地。串行 LVDS(低电压差动信令)输出减少了接口线路数量,减小了封装尺寸,从而进一步提高了密度。

ADS5271 可由内部或外部参照驱动,不过通过内部参照模式才能实现最佳性能与最简系统设计。该器件采用节约面积的散热增强型 PowerPAD、TQFP-80 封装。

由于 ADS5271 中的通道数量已经很高,因此该系列的未来产品将致力于提高采样率。这将通过过采样减少模拟滤波要求。

图3 ADS5271 功能结构图

测试测量:引脚电子技术

我们将自动测试测量 (ATM) 设备用于测试通信系统、计算机、工业系统以及许多其他最终应用中使用的半导体器件。接受测试的器件包括模拟、数字、混合信号、逻辑以及存储器等。为了对这些器件进行测试,我们应生成信号,激活被测试器件(DUT) 并测量响应。用于此目的的电子技术一般称作“引脚电子技术”,而且通常包括以下功能:

以任意电平将格式化数字模型驱动到 DUT;

从 DUT 读取数字模型,并以任意阈值水平获取定时测量结果;

动态设置 DUT 输出端口的负载条件;

强制电压并测量电流,以及强制电流,测量电压。

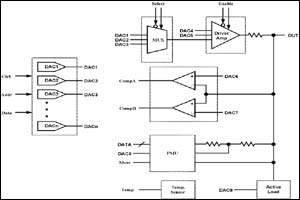

我们通过以下组件来实现上述功能,图 4 所示为功能结构图。

DAC

数模转换器 (DAC) 生成模拟信号,其用于驱动被测试器件,并用于实现各种功能,如设置窗口比较器、PMU 以及有源负载水平等。12 位或 13 位的分辩率较常见,而未来产品则要求 16 位乃至更高的分辩率。由于可编程信号和电平数量较多,因此我们需要大量 DAC 来实现完整的测试解决方案。

驱动器

为了实现正确测试某些器件所需的电平,需要一个驱动器放大器。驱动器放大器必须能够提供相关电压并具备 DUT 所要求的输出驱动功能。驱动器输出必须为三态输出,这样它才不会干扰从 DUT 返回的信号的测量。

窗口比较器

窗口比较器用于测试是否成功通过。测试存储器就是一个很好的使用实例,这时将数据模式写入 DUT 并被读出。

参数测量单元

参数测量单元可提供强制电压、强制电流以及测量电压与电流测量等功能。它可用于持续性测试,进行电压、输入电流以及漏电流测量。功能组合如下:

强制电压/测量电流 (FVMI);

强制电流/测量电压 (FIMV);

强制电压/测量电压 (FVMV);

强制电流/测量电流 (FIMI);

无强制/测量电压 (FNMV)。

有源负载

有源负载可用于提供 DUT 负载。通过 DAC 输入可对源极与汲极电流进行编程。

温度传感器

我们还包括了可提供温度信息的温度传感器。

图4 引脚电子技术功能结构图

引脚电子技术的未来趋势

到目前为止,引脚电子技术执行功能时需要彼此差异很大的技术--一种技术用于高速电路,而另一种技术则用于高精度直流 (DC) 电路,而且我们还要求采用不同的技术处理混合信号(如 DAC)功能。

尽管某些功能已经集成到了一起,而且目前也已经提供,但大多数解决方案都要求两到三颗芯片才能完全实现测试头。为了降低成本、提高功能引脚功能,并增加相同测试头数量下的引脚数量,我们应当进行功能集成,外部组件必须最小化,而且还应充分挖掘有关架构方面的改进。图 5 显示了我们所建议的一种引脚电子技术器件,其在同一芯片上集成了上述所有功能。

未来,这种芯片将用于减小测试解决方案的尺寸和成本,而这也将相应降低被测试器件的制造成本,此外,由于复杂性降低,这顺便也实现了提高可靠性的优势。

图5 集成的引脚电子技术

工艺技术实现了更高的集成度

有四种制造工艺可实现测试测量与医学成像领域更高的集成度,它们是:CBC-10、C05、BiCom II 以及 BiCom III。

CBC-10

TI 采用 CBC-10 工艺制造 VCA2611/6,这是一种 10V 互补双极晶体管模拟工艺,具备用于数字功能的 CMOS。

CBC 二极晶体管的特征尺寸仅为 1 _m (drawn),CMOS 电路的密度为 0.8 _m,是一种领先的工艺,为 NPN 以及 PNP 晶体管分别提供了 10GHz 和 7GHz 的截止频率。它还具备 80V 的典型尔利电压。此外,除了核心互补高速双极器件之外,其还采用了模块化方法来添加肖特基二极管、JFET 晶体管、高热能无源器件以及亚微米 CMOS 作为可选模块。

该工艺实现了高质量、低噪声的 JFET 晶体管,其可实现出色的高阻抗输入级。该工艺还具备可微调的薄膜电阻器以及高精度电容器,实现最小的寄生效应以及最佳的线性和跟踪性能。高精度电阻器与电容器实现的线性为每伏特数 ppm。举例来说,高精度电容器的线性比可为 5 ppm/V,电压系数为 10 至 50ppm/V。这就能够实现噪声与失真性能方面的显著提升。该工艺还为高密度 CMOS 电路提供了额外的隔离,提供了隔离构建电路的分开场所 (separate tub)。这对混合信号设计而言是至关重要的,因为这能够最小化串扰并改善精度,以及提高模拟电路的速度。这样,我们就实现了更高的精确度、更高的增益以及更快速的模拟电路。总而言之,CBC-10 工艺实现了数字控制、粘接逻辑以及与微控制器与 DSP 相连的接口。除了能在 ±5V 上运行高性能模拟与混合信号电路之外,CBC 还采用 0_5 V 的 CMOS 接口。

CBC-10 是一种非常快捷的模拟工艺,能够制造类似 OPA847 的放大器,其增益带宽乘积 (GBW) 达 3.9GHz,输入噪声低至 0.85nV/√Hz,转换速率高达 950V/_s,而且失真很低,只有-105dBc(5MHz)。模拟功能很强,CMOS 数字功能也很强,二者相结合就实现了更高程度的集成功能,正如我们在 VCA2611/6 中所述。

C05

ADS5271 采用 C05 数字工艺制造——该项工艺开发于 90 年代晚期,用于制造先进的 DSP(数字信号处理器)。目前其已是一种成熟的数字工艺,其模拟功能也在ADS5271 与 ADS5500 等产品中得到了进一步充分利用。

C05 是 0.18 微米的 CMOS 工艺,它实现了高传输时间的晶体管。其采用先进的金属系统来实现低结电容与晶体管周围的寄生元素。这使其理想地适应于高速混合信号设计。

C05 工艺还具备隔离式 NMOS,有助于降低数字开关带给敏感模拟节点的串扰,也可降低类似 ADS5271 的多通道部件中通道间的串扰。

我们采用智能架构与电路技术来充分发挥高 ft 晶体管的优势,从而设计出市场上最快速、性能最高的 ADC。

BiCom-II

BiCom-II 工艺是 15V 互补双极晶体管技术,其采用电介质隔离来降低晶体管中的寄生结电容。NPN 晶体管拥有 5GHz 的传输速率与 4GHz PNP,这就实现了快速而高性能的模拟晶体管。它能够处理更高的电压,这使其非常适用于要求更高电压的引脚电子技术。

此外,BiCom-II 还包括一个高性能 5 伏亚微米数字 CMOS 工艺,能够在芯片上实施包括数千个门极之多的逻辑功能。这种片上 CMOS 逻辑功能实施所要求的硅芯片面积更小,成本更低,比双极逻辑的功耗更低。因此,采用 BiCom-II 工艺制造的器件将支持片上 CMOS 逻辑功能,而其门密度则比前代互补双极工艺要高 20 倍。该工艺实现了集成在模拟块中的完整的标准数字函数库,并可使用标准的数字设计工具。

BiCom-II 工艺实现了多种底层工艺技术的最佳结合,非常适用于先进的引脚电子技术应用。BiCom-II 是互补双极与 CMOS 工艺的结合,其可提供出色的 beta 版,推出了优秀的双极晶体管尔利电压产品,并实现了更简单、更高性能的电路。15 伏互补双极工艺实现了用于运算放大器中的快速晶体管,成为多种模拟功能的构建块。CMOS 工艺提供了 5 伏模拟晶体管,实现了设计灵活性。上述因素可简化开发,并帮助 TI 以更快的速度响应市场需求,并推出全面集成的引脚电子技术产品。

THS4271 是模拟功能的一个实例。它具备 1.4GHz 的带宽,是第一款在保持极低噪声 (3 nV/√Hz) 条件下实现极快转换速率 (1000 V/_s) 的单位稳定增益运算放大器。

BiCom-III

BiCom-III 是一种 5V 硅锗 (SiGe) 工艺,其开发用于超高速模拟集成电路,是基于硅技术 (Si) 的电介质绝缘工艺,在基础区域添加了锗 (Ge)。在基础区添加锗大大提高了载体的移动性,并实现了极快的瞬态时间。该工艺实现了真正的互补双极 NPN 与 PNP 晶体管,传输频率 (fT) 达 18GHz,最高频率 (fmax) 达 40-60GHz。该工艺的速度比早期工艺提高了三倍。

与 BiCom-II 类似,BiCom-III 工艺流程也包括高密度亚微米 CMOS 逻辑,并具备广泛的数字库,可实现高性能模拟与复杂数字功能的无缝集成。

5V 超高速模拟晶体管使该工艺理想适用于测试低电压设备(如闪存)所需的引脚电子技术。

我们在说明有关 BiCom-III 工艺的先进性能时所举的实例就是 THS4304,其也是第一款 3GHz 单位增益稳定电压反馈运算放大器。根据设计,其可用于采用 +5V 单电源工作的高速、高性能模拟信号处理链中。

THS4304 可提供 3GHz -3dB 的单位增益带宽,830V/μs 的转换速率,在 20MHz 上 +45dBm 的输出三级拦截 (OIP3),2.8nV/√Hz 的输入噪声,以及 7.5ns 到 0.01% 的建立时间,同时静态耗电仅为 90mW。

全面集成:片上系统

制造商能够将高度复杂的高密度数字功能集成至模拟工艺上,或更准确地说,他们在成熟的数字工艺中开发了模拟功能,并推出了许多高性能片上系统 (SOC)。最新型的先进最高性能数字与模拟部件仍采用不同工艺进行开发,至少在不久的将来仍将保持这种状态。

在片上集成数字与模拟功能面临着诸多挑战。高性能数字逻辑会产生噪声,并降低模拟的信噪比 (SNR)。在同一 PCB(印刷电路板)上集成快速数字逻辑与模拟要求高超的工程设计技能,这甚至比芯片级集成还要困难。

先进的模拟电压最近已成功地从 12V 降至 5V 和 3.3V,但还不能很轻松地降至当前数字核心电压的水平。这是由于噪声与工作电压不成正比,而是基本保持常量。模拟工作电压必须保持足够高以实现良好的 SNR。较低的电压不能提供高动态范围模拟信号所要求的性能空间。

先进的数字工艺不包括高性能模拟组件。此外,先进模数之间在工艺特征尺寸方面也有很大差别。模拟工艺的起点是稳定的数字工艺。不管数字工艺晶体管的线性功能如何,我们都要用其实现片上模拟功能。即便如此,在工艺早期阶段,我们仍要强调数字部分;模拟功能只限于不需要额外工艺步骤或修改的部分。一旦工艺成熟并成功制造了最新系列的高速逻辑产品,数字工艺设计人员就可向下一工艺节点推进,而模拟组件设计人员则致力于在该工艺上推出更高的模拟功能。开发与完善模拟组件尚需时日。高性能模拟工艺通常比基本数字工艺的投产晚好几年。

结语

未来的竞争市场要求新工艺技术推动用于测试测量以及医学成像设备中高性能模拟组件的集成。这将拓扑技术发展与创新设计解决方案进行了完美结合,从而可进一步降低成本与功耗要求、缩小尺寸、提高可靠性,并使未来设备更轻盈小巧。

当前的技术实现了比以前任何时候都更高的集成度,但在同一器件上实施先进数字与高级模拟功能的真正集成还有待未来的发展才能实现。一旦能够实现真正集成,那么下一个目标就是降低成本。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)