摘 要:用CPLD在信息家电控制平台中设计键盘控制器。

前言

嵌入式系统中所用的键盘有编码和非编码键盘两种。编码键盘的优点是比较方便,亦不需要编写太复杂的程序。其缺点是使用的硬件较复杂。非编码键盘的按键是排列成行、列矩阵形式的,可以采用多种锁存器和可编程并行接口芯片组成,但是,在这些方法中,键盘扩展电路需要占用微处理器的资源对按键进行监控和处理,还有不能按照嵌入式设备中特定要求来进行开发,这些都制约了键盘在嵌入式设备中的开发应用。为了解决这一问题,本文提出一种利用复杂可编程逻辑器件设计技术实现键盘控制部分。

键盘时序信号和功能

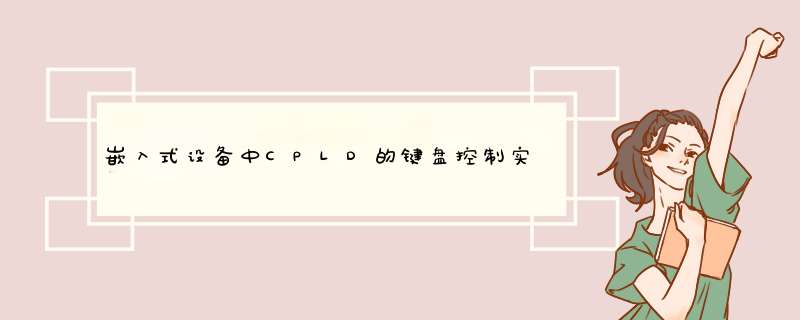

本设计采用通用键盘的实现形式。用户通过通用键盘向主机输送信息,使用的键盘方式只向主机单向传输数据,而不接收主机发送过来的数据。键盘输出的是扫描码,按串行方式输出。键盘输出的信号包括时钟信号和串行数据信号。键盘接口电路,按照串行传送的键盘代码的应答约定,接收键盘发送的扫描码,同时,还向键盘发送主机的控制信号,主机与键盘接口的连接信号时序如图1所示。

从时序图可以看出键盘控制器欲实现以下功能:产生按键扫描时序,并进行硬件去抖动,如果有按键按下,实现按键编码、中断处理等功能;可以同时处理数字键和功能键,对多个按键同时按下,采用一定的处理算法优先进行处理;提供数据显示接口,可以和我们采用的NEC公司NL3224BC35-20彩色显示器正确连接。

在本控制平台中根据系统要求对按键进行如下设置:数字键(0~9)、字母键(A~Z)、功能键(手动、自动、编程方式选择)、清零键(CLR)等共56个,排成8×7的键盘面板方式。

图1 CPU与键盘连接信号时序

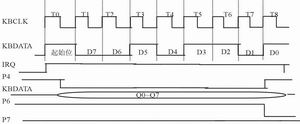

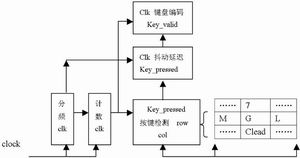

图2 键盘控制器结构框图

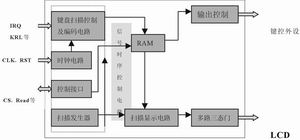

图3 键盘控制器的CPLD实现图

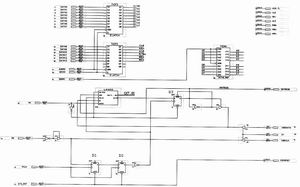

图4 VHDL语言实现键盘扫描控制示意图

键盘控制器结构和设计

按照上述设计要求,本控制器中应有:键盘扫描控制及编码电路,分行实时扫描按键的状态信号,如果没有按键被按下,则扫描下一行,如果有按键被按下,则控制器锁定被扫描行,然后进行键盘抖动处理,确定是 *** 作按键后,进行相应的处理;键值存放RAM中数据容量设定为16位;扫描显示输出控制电路,用来驱动NL3224BC35-20连接信号电极;接口控制电路,主要相应CPU的时序和对地址和数据线进行处理。其结构框图示于图2。

为了实现上述的控制器功能结构,利用可编程逻辑技术对各个功能块进行逻辑的时序描述和实现。程序的设计主要采用了图形设计方法,其中大部分的元件应用VHDL语言编程来制作,一些简单通用的元件使用Max PlusⅡ所提供的器件,最后再把它们按照图3的系统框图连接。

根据结构框图可知道,由于S3C4510B的时钟频率50MHz,键盘扫描不需要那么高的频率,所以要进行分频处理,将频率降到1KHz;计数器产生循环扫描信号,用来控制按键监测和键盘编码;由分频器的时钟信号则可以实现约10ms的去抖动延时。整个设计思路,便于用硬件描述语言(VHDL)对上述设计进行描述(见图4)。

由于在系统中,还考虑了SMART卡接口电路的设计,根据设计要求采用的CPLD芯片为EPM7128AELC84-5。在本控制平台使用中键盘接口芯片性能稳定,既满足了键盘控制的要求,又实现了高速SMART卡的传输需求。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)