引言

数字高清晰度电视(HDTV)是继黑白电视和彩色电视之后的新一代电视,HDTV接收机或机顶盒具有广阔市场和巨大经济效益,已经成为国际高科技领域研究开发的热点之一。

HDTV接收系统由信道解码、信源解码、显示终端组成。目前,多数HDTV信源解码方案均由三片或三片以上的核心芯片组成,分别用于系统控制+解复用、视频解码、音频解码。为了提高系统的集成度,信源解码方案正向着两片方案过渡,最终可能实现单片解码方案。本文提出一种两片解码方案:用TI的TMS320C6701完成系统控制、解复用、音频解码;用STI7000完成视频解码。

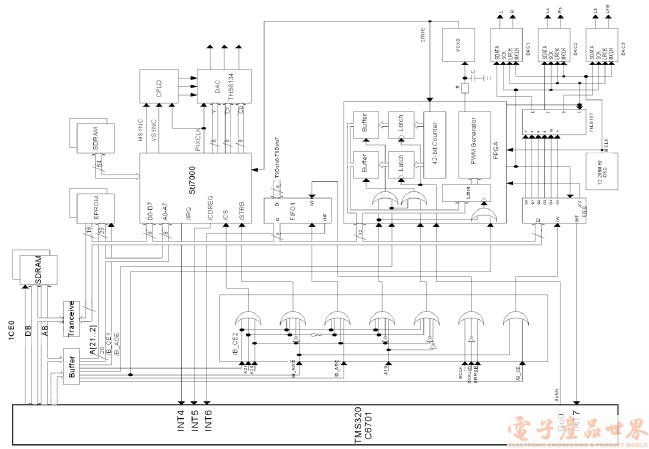

图1 信源解码器硬件框图

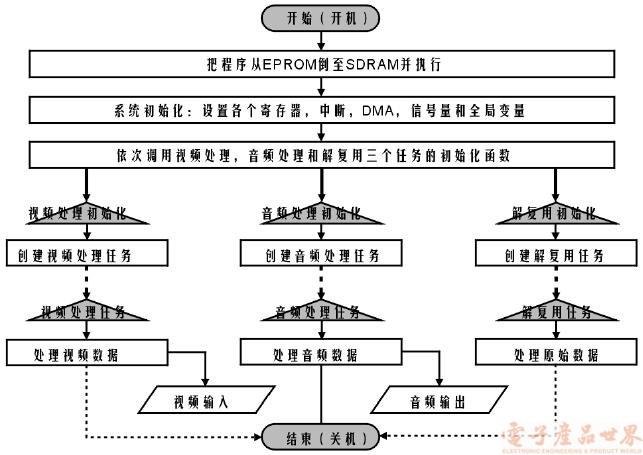

图2 信源解码器软件结构框图

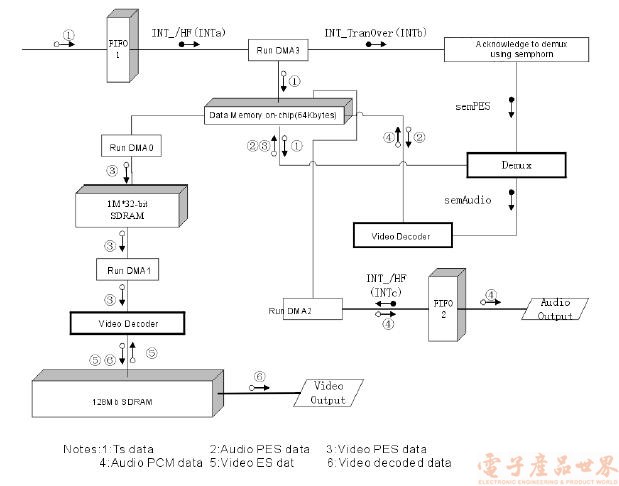

图3 软件解码数据流图

硬件设计

本信源解码方案的硬件设计如图1所示。

系统的核心为TMS320C6701 DSP,采用EPROM固化系统程序。C6701配接SDRAM用来存储数据和工作程序。FIFO1用来输入TS。视频解码器STI7000映射到C6701存储空间。STi7000配有SDRAM用来存储视频PES、各种图像(解码、参考和显示帧图像)及OSD数据。视频后处理部分由THS8134 DAC、CPLD及运放组成。系统本地时钟和PWM产生器由FPGA实现,它与VCXO、RC低通滤波器一起在C6701解复用软件配合下完成27MHz时钟恢复。音频解码由C6701软件完成。音频输出部分由FIFO2、一个 74LS157和三个D/A芯片组成。音频输出所用时钟和控制信号也由FPGA实现。

系统控制、解复用和音频解码

C6701是TI的高性能浮点DSP,时钟为167MHz,具有1336MIPS能力。C6701的Memory Map选为Map0。在其存储器的 CE0 空间中放置了1M*32位的SDRAM。在CE1空间放置了1M*16位EPROM。本系统使用ROM boot process,因此C6701的BOOTMODE[4:0] 引脚置为“10010”。C6701的程序超过64K字节,因此从0地址开始执行的是一个Loader,它把EPROM中其他程序继续传送到SDRAM中。传送完成后,CPU开始从Loader以下的地址开始执行程序。CE2空间用来放置异步器件,此时它的大小为4Mbytes。它被GAL内部的译码器等分为四个部分。前两个部分放置STi7000;第三部分放置FIFO1;第四部分放置实现本地时钟和PWM的FPGA。CE3空间仅放置FIFO2。

C6701 PLL模式被选为 *4 , 即输入引脚CLKMODE[1:0] = 11b。41.75MHz由5V晶体振荡器产生,经过LVT125做电平变换后输入给C6701。C6701的SDCLK输出加给零延迟时钟缓冲器CY2308后分两路分别提供给SDRAM。C6701所用的3.3V(VCC3)和1.9V(VCC1.9)由PT6921产生。本系统有一个 14脚插座, 它可与XDS510 emulator(硬件仿真器)连接起来实现仿真。C6701的HPI和串口1不被使用,相应引脚与跳线连接,以便系统功能扩展时使用。

本系统输入为并行TS,输入接口由TS数据(TSData[7:0]),DVALID,BCLK and ERROR组成。当TS数据输入达到2KB时,FIFO的/HF信号有效,它作为一个中断信号加给C6701 INT6脚。接到此中断后,C6701运行有关中断子程序,DMA将2KB TS数据取出传输到C6701片内的SRAM中。该FIFO映射到C6701 EMIF CE2空间。

27MHz系统时钟恢复由FPGA(EPF10K20)中的计数器/PWM模块、外部低通滤波器和VCXO在C6701相应软件的控制下完成。VCXO输出的时钟信号输入给FPGA中的一个42位计数器产生本地时钟LMCR。当C6701按一定算法求得PCR与本地时钟的差值后,将此差值输出给FPGA的PWM模块,该模块将此差值转换为PWM信号后输出给低通滤波器,取出直流后控制VCXO输出频率。经一定时间的调整后,得到与发射方同步的27MHz。VCXO输出的27MHz时钟也提供给视频解码器使用。

视频解码

视频解码由ST公司的STi7000在C6701的相应软件控制下实现。STi7000完成如下功能:a)接收C6701传来的视频PES并进行句法分析,取出ES存入SDRAM,取出DTS、PTS存入相应寄存器。b)找到ES中各层的开始码并提取头部信息,存入相应寄存器中,发中断给C6701。C6701读取这些头部信息,并据此控制解码流水线工作。c)STi7000的核心是硬件SLICE层以下解码流水线。它从SDRAM中读出ES,进行解压缩(VLD-反扫描-IDCT-运动补偿)得到重构图像,并根据其类型(I、B或P帧)存入SDRAM相应区内。在流水线开始每一帧图像解码前,C6701要根据该帧类型等参数向STi7000发解码命令。解码流水线另一个重要功能是实现隐错。d)视频格式转换:图像输出前,可进行各种格式变换(水平分辨率上下变换;垂直行数上下变换;隔行(I)和逐行(P)相互变换;3:2电影下拉模式和幅型比(4:3或16:9)变换(FULL、ZOOM、LETTERBOX和SIDEBAR)。e)实现OSD功能。

STi7000约有110个寄存器,分为配置、控制、存储器存取、解码指令、显示、OSD、时钟/锁相环、D1接口、PES等9类。 C6701对STi7000各寄存器的存取通过STi7000的8位微控制器接口进行。该接口映射入C6701 EMIF CE2空间最低1MB内。其8位数据线接到LVT16245一边;8位地址线接LVT16244输出边;片选(notA_cs)接GAL相应的输出,读写(A_RnotW)接LVT16244输出/B_AWE上。中断请求信号(notA_IRQ)接C6701 INT4脚。C6701通过STi7000的8位并行数据接口向STi7000写入视频压缩数据。该接口与上述8位微处理器接口共用8位数据线。压缩数据请求信号接C6701 INT5脚。压缩数据选通输入notA_STRB则由GAL提供。

STi7000需要128Mbit的SDRAM存储器,由两片4*512K*32-Bit的100MHz SDRAM芯片组成。STi7000要求SDRAM具有如下特点:全页Burst长度;连续Wrap;3周期CAS Latency。SDRAM和STi7000实现“glueless(无胶合)”连接。

本系统采用TI的THS8134实现视频输出D/A变换。本系统只实现HD输出方式。STi7000的24Bit Y、Cb、Cr数字视频信号和PIXCLK直接输出给THS8134,产生模拟Y、Pb、Pr分量信号。STi7000的PIXCLK、HSYNC和VSYNC信号加给一个CPLD(EPM7128)。该CPLD控制THS8134按照相应的标准(1080I格式对应SMPTE274M;720P格式对应SMPTE296M;480P格式对应SMPTE293M;480I格式对应SMPTE170M)分别在Y、Pb、Pr分量上叠加三电平(1080I和720P)或两电平(480P)复合同步信号,然后经运算放大器放大后输出。这四种格式由C6701 TOUT0和TOUT1输出的Displaymode0和1选择。

当音频开始输出时,C6701先将4KB数据写入FIFO2中。FIFO2映射入C6701 EMIF CE3空间。FIFO2的满标志/FF信号有效,它触发FPGA内相应模块开始工作,将音频主时钟12.2880MHz时钟分频产生LRCLK(左右时钟信号,频率48KHz)和SCLK(串行时钟,频率为3.072MHz)。SCLK信号作为FIFO2的读信号,而LRCLK则作为74LS157的输入选择信号。当LRCLK为高电平时,左(左环、中央声道)数据输出给三个DAC芯片;当LRCLK为低电平时,右(右环、LFE)数据输出给三个DAC芯片。MCLK、LRCLK和SCLK同时输入给三个DAC芯片。由三个DAC输出的5.1声道经放大后分别输出。当FIFO2中已输出2KB数据时,其/HF无效,此信号接至C6701 INT7输入脚,触发该中断。C6701执行相应的中断子程序,再向FIFO2输出2KB数据,如此循环,保证音频信号持续输出。

软件设计

系统的软件结构如图2所示。

在C6701内部有64Kbytes的数据SRAM和64Kbytes的Cache/Program SRAM。程序SRAM经初始化用作Cache。64K字节的片内数据RAM被组织成两个块。它们的地址分别为8000 0000h到8000 7FFFh和8000 8000h到8000 FFFFh。当CPU的Side A和Side B或者DMA控制器同时使用不同块时,不会引起冲突。因此,同时访问的数据位于不同块时,不需考虑它们的地址。整个片内数据RAM分为五个部分:TS_Buffer(4K字节)用来缓冲输入的TS;V_PES_Buffer(16K字节)用来存放视频PES; A_PES_Buffer(8K字节) 用来存放音频PES/ES; A_Buffer(32K字节) 用来存放解压缩后的音频数据;剩余的部分用于缓存中间计。

算数据。每一部分Buffer又分成两个块,以乒乓方式使用。即一块由CPU使用时,另一块可以同时进行存贮或由DMA使用。

软件整个系统解码数据流图如图3所示。首先FIFO1接收到的TS数据到其存储量的一半(2KB),发出中断(INTa)激活DMA3。DMA3把FIFO1里一半的数据倒到C6701的片内存储器TS_Buffer中,并在传输完成时发出中断(INTb),INTb的中断服务程序发出信号semPES激活解复用任务。解复用任务从片内存储器中取出TS数据进行相应处理,然后把分离出的音视频PES数据送回片内存储器,当A_PES_Buffer填充一半时,通过信号量semAudio激活音频处理任务。音频处理任务从A_PES_Buffer中取出音频PES数据,解码后存到A_Buffer。当A_Buffer中的数据积累到一定数量时,激活DMA2。DMA2把解码后的4KB音频数据输出给FIFO2,FIFO2的/FF信号(满标志)启动音

频数据由FIFO2的读出。音频输出FIFO2半空时会发出中断INTc,激活DMA2。DMA2把A_Buffer中的数据再传送2KB到FIFO2去,如此继续下去。视频PES数据由DMA0从V_PES_Buffer不断地倒到片外SDRAM中,当接到STi7000请求时,激活DMA1,把SDRAM中缓存的的视频PES数据输出给STi7000,进行解码,然后,经视频后处理后输出给显示器。

解复用的功能包括:PSI分析,时钟恢复以及对传输包拆包并传给相应的buffer(缓存器)。

视频解码的功能是对视频PES进行解压缩,恢复出视频流。在系统中,Video Driver的中断的优先级被设为最高。视频解码系统主要是通过中断来触发其它过程的进行,中断是视频解码主线, *** 纵着整个视频解码的过程。

音频解码的功能是对音频PES进行AC-3解压缩,恢复出音频流。音频解码从音频PES包解码开始,在6701片内的数据存储区中开辟A_PES_Buffer(由两块各4KB对称的存储区组成),解复用得到的音频PES数据以乒乓方式存储到这两个区域。经过拆包PES数据得到的ES数据直接覆盖PES数据所处区域。然后开始音频解码的核心计算,将解码输出的PCM数据格式化后存储到片内数据存储区中开辟的两块(各16K)PCM缓冲区中,利用DMA2将其中的数据输出给片外的FIFO。

结语

本论文提出了一种基于通用DSP C6701的HDTV信源解码器两片解决方案。随着技术的进步,将来可能会提出HDTV信源解码器单片解决方案。即在单个功能强大的芯片的基础上,很多工作可以由软件控制实现。本论文提出的HDTV信源解码器解决方案对于下一代HDTV信源解码器的研制具有重要的参考价值。

欢迎分享,转载请注明来源:内存溢出

赞

(0)

打赏

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

在嵌入式系统中实现从RAM快速引导技术

上一篇

2022-08-01

TMS320C55x嵌入式实时多任务系统DSPBIOS&n

下一篇

2022-08-01

评论列表(0条)