LeonardoSpectrum 是Mentor Graphics公司设计的功能强大的EPLD/FPGA/ASIC综合工具,支持大部分EPLD/FPGA厂商的产品。LeonardoSpectrum支持VHDL、Verilog、EDIF的综合、优化和定时分析,可以运行在Windows 98/2000/NT/XP和HP、SUN 的UNIX平台上。

LeonardoSpectrum通过名为exemplar的库,可以在用HDL设计FPGA/EPLD时使用与原理图设计相同的功能。LeonardoSpectrum对于Xilinx公司的EPLD/FPGA支持尤其完善,使得用HDL的设计在效率和功能上可以和原理图的设计相当。本文总结了使用LeonardoSpectrum过程一些有用的设计方法。

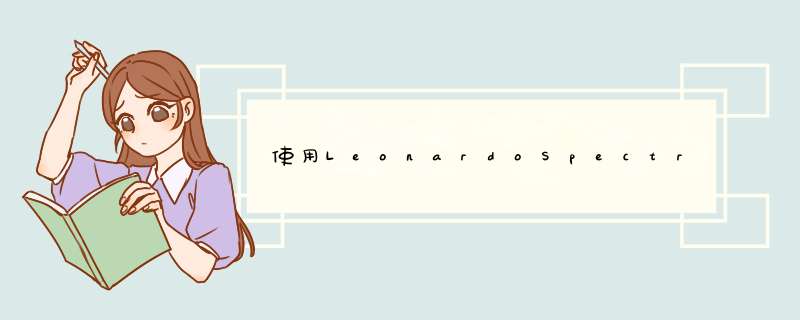

图1 全局时钟使用的map结果

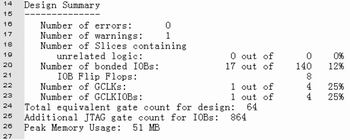

图2 延迟锁相环使用map结果

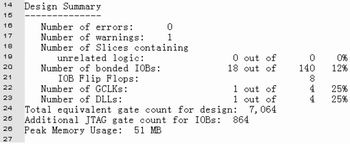

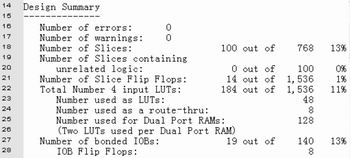

图3 块状RAM的map结果

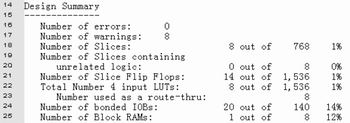

图4 分布式RAM的map结果

属性的使用

在LeonardoSpectrum中,可以在程序中对信号赋予属性来对综合结果进行控制。在使用LeonardoSpectrum综合时,除了LeonardoSpectrum提供的属性外,可以把Xilinx原理图设计中的某些元件作为属性来赋予信号,主要限于双端口的元件,例如IBUFG,BUFG等等。LeonardoSpectrum所提供的属性可以参看使用手册。

如果使用LeonardoSpectrum来综合,建议调用exemplar库,以获得更多的功能支持,本文介绍的程序都需要使用exemplar库。下面是对程序中一个信号通过赋予bufg的属性而定义该信号为全局时钟的例子。

......

ARCHITECTURE rtl of bufg IS

SIGNAL clk :td_logic;

attribute buffer_sig of clk: signal is "bufg";

BEGIN

clk<=clkin;

clkout<=clk;

process(clk)

begin

if(clk'event and clk='1') then

end if;

end process;

END rtl;

这个程序选用的芯片是Xilinx的spartanII 系列XC2S50-5QP208,经LeonardoSpectrum综合后,用Xilinx ISE5.1进行map后的结果如图1所示,可以看到使用了1个全局时钟。

元件的引用

在Xilinx的FPGA/EPLD的原理图设计中需要用到元件库,元件库中包含一些特殊功能的元件,例如延迟锁相环(DLL)、全局时钟BUF、边界扫描电路、数字时钟管理器(DCM)、内置SRAM等。LeonardoSpectrum提供的exemplar库中的程序包使得设计者可以在VHDL程序中直接引用原理图库中所包含的元件。引用元件时,先调用exemplar库,对要引用的元件按照原理图库中的描述进行声明。引用元件时可以只使用其中一部分参数,不必对元件所有的参数进行映射。

下面是引用Xilinx的FPGA的延迟锁相环〔DLL〕的例子。

............

ARCHITECTURE rtl of pll IS

SIGNAL clk :std_logic;

component clkdll --锁相环

port(clkin,clkfb,rst :in std_logic;clk0,clk90, clk180,clk270,clkdv,locked :out std_logic);

end component;

BEGIN

CLK1: clkdll port map(clkin=>clkin,clkfb=>clk,rst=>'0', clk0=>clk,clk90=>clkout );

process(clk)

begin

if(clk'event and clk='1') then

data_out<=data_in;

end if;

end process;

END rtl;

这个程序也选用Xilinx的XC2S50-5QP208,经LeonardoSpectrum综合后,用Xilinx ISE5.1进行map后的结果如图2所示,可以看到使用了一个DLL。

RAM的综合

RAM设计是Xilinx FPGA的一个特色,按照在芯片内的分布情况可以分为分布式RAM和块状RAM,分布式RAM分布在每个LC中,可以将一个LC作为16×1的同步RAM使用,也可以将两个LC联合起来作为16×2、32×1的同步RAM或者16×1的双口RAM使用,块状RAM是专用的分布FPGA边缘的RAM块。RAM使用时又可以作为ROM,单口RAM、双口RAM等。如果是原理图设计,可以在选择元件时选择不同的元件来选择不同类型的RAM,但是对于用描述语言来进行RAM设计时,就需要综合工具的支持,不同的综合工具,对相同的语句,可能就综合成不同类型的RAM。LeonardoSpectrum对VHDL的支持达到相当的高度,除了提供属性的方法来使用分布式RAM和块状RAM外,还可以在设计时使用不同的描述语句来产生分布式RAM和块状RAM。下面是一个综合成块状RAM的例子。

......

ARCHITECTURE rtl of blockram IS

TYPE RAM IS ARRAY ( 0 TO 127 ) OF STD_LOGIC_VECTOR( 7 DOWNTO 0 );

SIGNAL testram :ram;

SIGNAL cc1,cc2 :std_logic_vector(6 downto 0);

SIGNAL addr1,addr2 :integer range 0 to 127;

BEGIN

......

process(clkout) --从RAM中读出数据

begin

if(clkout'event and clkout='1') then

data_out<=testram(addr2);

end if;

end process;

END rtl;

该程序也选用Xilinx的XC2S50-5QP208,经LeonardoSpectrum综合后,用Xilinx ISE5.1进行map后的结果如图3所示,可以看到生成了块状RAM。

下面程序是综合成分布式RAM的例子。

......

ARCHITECTURE rtl of disram IS

TYPE RAM IS ARRAY ( 0 TO 127 ) OF STD_LOGIC_VECTOR( 7 DOWNTO 0 );

SIGNAL testram :ram;

SIGNAL cc1,cc2 :std_logic_ vector(6 downto 0);

SIGNAL addr1,addr2 :integer range 0 to 127;

BEGIN

......

process(clkout) --从RAM中读出数据

begin if(clkout'event and clkout='1') then

if(ramsel='1') then data_out<=testram(addr2); end if; end if;

end process;

END rtl;

选用XC2S50-5QP208,经LeonardoSpectrum综合后,用Xilinx ISE5.1进行map后的结果如图4所示,可以看到生成了分布式双口RAM。

比较上面两段程序,可以看到它们的差别就在于生成分布式RAM的程序中,数据输出时有一个selram信号,也就是说,如果直接用时钟读出RAM中的数据,就综合成块状RAM;如果是用带使能的方式输出RAM中的数据,就综合成分布式RAM。

结语

综上所述, LeonardoSpectrum对于用VHDL写的用于Xilinx FPGA的程序支持是非常到位的,可以充分利用Xilinx的优势,用语言设计出与原理图设计相当功能的程序。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)