OMAP5910简介

OMAP5910处理器是由TI应用最为广泛的TMS320C55x DSP内核与低功耗、增强型ARM925微处理器组成的双核应用处理器。C55x系列可提供对低功耗应用的实时多媒体处理的支持;ARM925 MPU 可满足控制和接口方面的处理需要。基于双核结构,OMAP5910同其他OMAP处理器一样,采用开放式、易于开发的软件设施,支持广泛的 *** 作系统,如Linux、Windows、WinCE、Nucleus、Palm OS、VxWorks、Java等,优化其应用程序时可以通过API及用户熟悉且易于使用的工具。

图1 硬件构成方案

图2 软件构成方案

OMAP5910的结构

TI925T(ARM9TDMI)内核

TI925T(ARM9TDMI)内核采用5级管道化流水线32位RISC处理器架构的体系结构,ARM9内核,同时配备Thumb扩展。它能够处理32位或者16位的指令和8位、16位、32位的数据,这款新型高性能、低功耗的微构架兼容ARMv4T指令集,并通过使用协处理器CP15使体系结构得到增强。系统中的控制寄存器可通过对协处理器CP15的读写来对MMU、cache和读写缓存控制器进行存取 *** 作。这种微构架在ARM核的周围提供了指令与数据存储器管理单元,指令、数据和写缓冲器,性能监控、调试和JTAG单元以及协处器接口,MAC协处器和内核存储总线。

TI925T 的MMU具有两个64项的转换旁路缓存器(TLB)用于指令和数据流,每项均可映射存储器的段、大页和小页。为了保证内核周期的存取指令和数据,TI925T包含了分别独立的1个16KB字节的指令cache和8KB字节的数据cache。指令和数据cache都是2路相互关联的cache,以16字节为一块进行 *** 作,并采用最小最近使用(LRU)算法以刷新存储。另外,TI925T还提供一个写缓冲用于提升内核性能,其能够缓冲数据容量高达17字。

TMS320C55x (C55x)内核

C55x内核的主要特点是:有1个64×8位缓存队列,2个17×17位乘法器,1个40位ALU,1个16位ALU,1个40位桶形移位器和4个40位加法器。另外还有12条独立的总线,即:3条数据读总线,2条数据写总线,5条数据地址总线,1条程序读取总线和1条程序地址总线,以及用户可以配置的IDLE域。同时,内核主要由4个单元组成:指令缓冲单元(I单元)、程序流单元(P单元)、地址数据流单元(A单元)和数据运算单元(D单元)。

系统控制功能

OMAP5910的系统控制模块提供了实时时钟(RTC)、看门狗(WT)、中断控制器、功率管理控制器、复位控制器和两个片上振荡器。

时钟和电源管理

OMAP5910提供了2个振荡器来辅助管理电源耗损,设计系统时,在待机模式下可以直接关闭12MHz的振荡输入,只留下32KHz振荡器来维持系统运作。

电源管理提供了3种工作模式:Awake模式、Big sleep模式和Deep sleep模式。Awake模式下,整个芯片运行在峰值频率,32kHz振荡器和12MHz振荡器正常工作,在时钟请求时,能使能外围器件的12MHz时钟,并由ULPD DPLL或APLL产生48MHz时钟;当芯片产生IDLE请求时,芯片工作在Big sleep模式下,DPLLs 1、内部12MHz时钟被关闭;Deep sleep模式下,只有32KHz振荡器正常工作,整个系统将处于最低功耗状态。

EMIFS接口、EMIFF接口、IMIF接口和存储器

在OMAP5910微处理器核心中,提供了两个扩充内存接口。一个扩充内存EMIFS接口可以支持128MB的ASRAM、FLASH和ROM。另一个扩充内存EMIFF接口可以设定为用来 *** 作SDRAM,寻址空间高达128MB。另外还有一个内部存储器区,用来连接OMAP5910微处理器内部的内存,可以用以常用的数据存取,比如说用作微处理器液晶屏幕显示的图像缓冲器。这几个内存接口都是独立运作,可以同时经由微处理器核心存取数据,又可以利用DMA数据。而内存间数据传输的控制则由流量控制器(TC)来控制,它会对各种传输需求依设定的优先级来执行数据的传送。

外围控制模块

OMAP5910微处理器拥有9个独立通道和7个接收/发送端口的DMA控制器。DMA控制器可响应内部和外部设备的请求,在MPU TI925T(ARM9TDMI)运行的条件下,完成外部寄存器、内部寄存器和外部设备之间的数据传输。系统DMA的设置决定取决于MPU TI925T(ARM9TDMI)内核。

OMAP5910微处理器另外有一个独立DMA通道供给LCD控制器专用。LCD控制器可支持单色和彩色STN以及彩色TFT显示。显示分辨率最大为1024×1024像素。在单色模式下,能支持15级灰度;在STN彩色模式下,最高支持3375种颜色;在TFT显示模式下,最高支持65536种颜色。LCD控制器将帧缓存中的像素编码值,对应12位宽的256个入口的调色板RAM,根据数据宽度决定彩色的数量。通常可选用片内共享的SRAM或者通过EMIFF接口选用外部SDRAM来当作帧缓存器,为优化性能推荐选用片内共享的SRAM。

OMAP5910微处理器支持的串口包括:基于通用串行总线2.0版本和开放式主机控制接口1.0a版本的USB Function and Host模块接口;3个通用异步收发口(UART),其中两个UART具有自动调节波特率的性能,其波特率调节范围在1200bit/s~115.2Kbit/s之间,而另外一个URAT通常当作一般的URAT或者可用作IrDA接口使用;3个多通道缓冲串行口(McBSP),可提供高达128个通道的高速、全双工通信的串行接口,可直接与T1/E1调帧器相连接,并支持兼容MVIP、ST-BUS、IOM2、AC97、I2S等协议的设备;2个多通道串行口(MCSI),提供了全双工通信以及对主/从时钟的控制功能,同时,为C55x 内核对外部设备诸如多媒体数字音频解码编码器或其它模拟转换器等的访问提供便利的通信接口;基于Philips I2C-BUS 2.1版本的I2C Master/Slave接口,支持多主机(Multimaster)模式,即在I2C总线上的设备(包括OMAP5910在内)都可充当接收机或发送机;1个支持MMC/SD或SPI协议并传输串行数据的MMC/SD卡接口和1个SPI接口。

OMAP5910在语音

识别中的应用

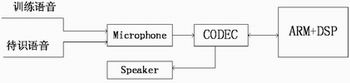

硬件构成方案

硬件主要由TI公司生产的CODEC数字音频解码编码器(TLV320AIC23)、OMAP5910 (ARM9TDMI+C55XTM)开放多媒体应用芯片及电源芯片等构成。构成方案如图1所示。

训练语音和待识语音通过话筒,经过CODEC预处理、数据采集后变成离散数字信号进入DSP,由DSP对离散的语音信号进行如下的计算处理:端点检测、分帧;特征值提取,分别形成训练模板和标准模板;使用某种搜索算法搜索最佳匹配;最后由ARM控制整个系统,输出识别结果。

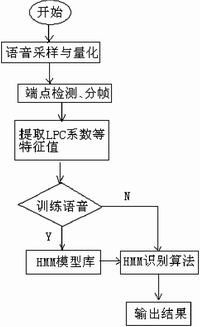

软件构成方案

语音识别的最终目的是实现大词汇量、连续语音、非特定人语音识别,这里我们选择用HMM模型来进行语音训练与识别。软件构成方案如图2所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)