ad9959应用控制电路

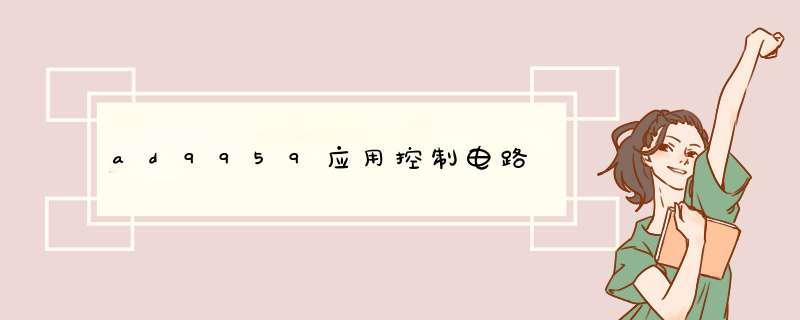

AD9959可以实现最多16电平的频率、相位和幅度调制,还可以工作在线性调频、调相或调幅模式。AD9959的应用范围包括相控阵列雷达/卢纳系统、仪表、同步时钟和RF信号源。AD9959的内部结构如图1所示,主要特性如下:

◇有4路带10位DAC的DDS通道,最高取样频率为500 MSPS;

◇大于65 dB的通道隔离度;

◇32位频率分辨率;

◇14位相位失调分辨率;

◇10位输出幅度可缩放的分辨率;

◇具有增强数据吞吐量的串行I/O口(SPI);

◇可软件/硬件控制以降低功耗;

◇双电源(DDS核1.8 V,串行I/O3.3 V);

◇内置多器件同步功能;

◇内置时钟倍频锁相环(4~20倍倍频)。

2 AD9959的引脚功能

AD9959采用56脚LFCSP封装,各引脚的功能定义如下:

SYNC_IN:输入引脚,可同步多片AD9959。使用时应与主AD9959的SYNC_OUT相连;

SYNC_OUT:输出引脚,可同步多片AD9959,使用时应与从AD9959的SYNC_IN相连;

MASTER_RESET:复位输入引脚,高有效;

PWR_DWN_CTL:外部电源掉电控制引脚;

AGND:模拟地;

DVDD:数字电源(1.8 V);

DGND:数字地;

DAC_RSET:输入引脚,可为DAC设置参考电流,使用时应通过一个1.91 kΩ电阻接地;

REF_CLK和REF_CLK:参考时钟或振荡输入端(互补输入),如果使用单端输入方式,则应从REF_CLK引脚连接一个0.1μF的解耦电容到 AVDD或AGND;

CLK_MODE_SEL:振荡器部分控制引脚,接高电平时,电压不要超过1.8 V,接低电平时,振荡器被旁路;

LOOP_FILTER:输入端,使用时应串联一个零电阻和680 pF电容至最近的AVDD脚(Pin28);

I/O_UPDATE:输入引脚,通过该脚的上升沿可把串行口缓存的数据内容送至激活的寄存器中,I/O_UPDATE信号应与SYNC_CLK信号保持同步,并须满足建立时间与保持时间的要求;

CS:片选串口使能信号端,低有效;

DVDD_I/O:3.3 V数字电源;

SYNC_CLK:时钟输出,为内部时钟的1/4,用于同步I/O_UPDATE信号;

SCLK:I/O串行 *** 作时钟输入端,在该端的上升沿写入数据,下降沿读出数据;

SDIO_0:双向引脚,用于串行 *** 作的数据输入和输出;

SDIO_1:3:双向引脚,用于串行 *** 作数据输入输出,也可用于控制DAC输出幅度的斜率;

P0~P3:输入引脚,这四个引脚用于控制调制方式的选择,扫描累加器的开关或者输出幅度的升降斜率。该四个引脚中的任何一个引脚信号的变化都等同于一个I/O_UPDATE信号的上升沿,该端须与SYNC_CLK信号保持同步,并须满足建立时间与保持时间的要求;

CH0_IOUT ~CH3_IOUT, CH0_IOUT ~CH3_IOUT:输出引脚,四个通道的互补输出端,使用时,需接上拉电阻至AVDD。

3 工作模式组合

AD9959所具有的的四通道可以使其同时实现多种工作模式的组合。但是,在某些模式下,则需要几个数据引脚来实现特殊功能,这就限制了组合方式。根据AD9959芯片的资源,可同时实现的工作模式组合如下:

(1) 四个通道可以实现单频模式、2电平调制模式和线性扫描模式的任意组合,每个通道均可工作在这三种模式中的一种;

(2) 可以同时有一个或两个通道工作在4电平调制模式,余下的通道工作在单频模式;

(3) 可以有一个通道工作在8电平调制模式,余下的通道工作在单频模式;

(4) 可以有一个通道工作在16电平调制模式,余下的通道工作在单频模式;

(5) 单频模式下,可以控制每个通道的输出幅度斜率;

(6) P2和P3引脚用于控制输出幅度斜率时,任意两个通道可同时工作在2电平调制模式,也可同时工作在线性调频或调相模式;

(7) P3引脚用于控制输出幅度斜率时,可以有一个通道工作在8电平调制模式,余下的通道工作在单频模式;

(8) SDIO_1~SDIO_3引脚用于控制输出幅度斜率时,四个通道可以实现各种2电平调制模式的组合,而未用于2电平调制模式的通道则可工作在单频模式;

(9) SDIO_1~SDIO_3引脚用于控制输出幅度斜率时,可以同时有一个或两个通道工作在4电平调制模式,其余通道工作在单频模式;

(10) SDIO_1~SDIO_3引脚用于控制输出幅度斜率时,可以有一个通道工作在16电平调制模式,其余通道工作在单频模式;

(11) 幅度调制、线性幅度扫描和控制输出幅度斜率功能不能同时实现,但频率和相位调制则可与控制输出幅度斜率功能同时实现。

4 串行 *** 作

AD9959的四个通道可共享一组寄存器地址,这种地址共享机制其得可以同时向四个通道的配置寄存器写入相同的数据。当需要对四个通道进行不同设置时,可以通过设置通道使能位来各自独立地写入每个通道设置的数据。

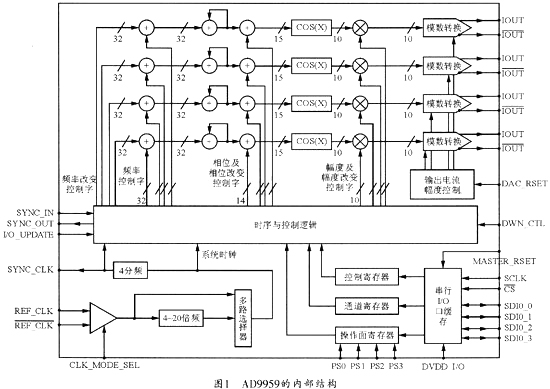

一个串口通信周期分为指令周期和数据读写周期两个阶段。首先传送指令阶段的8位指令字,对应于SCLK的8个上升沿,然后执行由指令设定的1~4个字节的数据读写,完成后再等待下一个指令周期的到来。

AD9959的串口 *** 作与ADI公司之前推出的DDS芯片基本一致,但由于AD9959有四个串行数据引脚(SDIO_0:3),因而其编程具有更大的灵活性,通过配置相应的寄存器可以有四种编程方式进行串行I/O *** 作。分别是单bit两线模式,单bit三线模式。双bit模式和四bit模式。

设置为单bit两线模式时,SDIO_0为双向数据引脚。设置为单bit三线模式时,SDIO_0为数据输入引脚,SDIO_2为数据输出引脚。在这两种模式下,SDIO_3都作为串口同步恢复信号引脚,通过一个正脉冲使串口恢复为初始等待指令状态。图2给出了单bit两线模式的串口写时序。

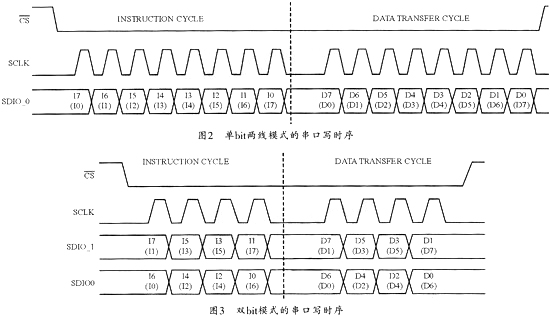

设置为双bit模式时,SDIO_0和SDIO_1同时作为双向数据引脚,每个SCLK周期传输两位数据,这样,传送一个八位的数据信息只需要四个SCLK周期,SDIO_3仍作为串口同步恢复信号。图3给出了双bit模式的串口写时序。

设置为四bit模式时,SDIO_0:3可同时作为双向数据引脚,每个SCLK周期传输四位数据,故传送一个八位数据信息仅需要两个SCLK周期。

5 在雷达中频信号模拟器中的应用

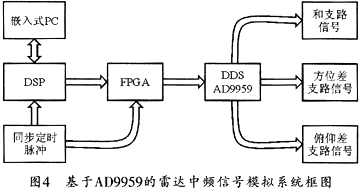

现代雷达信号模拟器的设计偏重于运用数字化方式来实现。事实上,随着实时数字信号处理技术的发展,PC+DSP+DDS的体系结构已成为雷达信号模拟器实现的主要方式。而AD9959由于在一块芯片上集成了四个DDS通道,因此,AD9959的使用可为多路雷达信号模拟器的设计提供了极大的方便。因为它可使得原本需要多片单通道DDS芯片的系统,现在只需一片AD9959即可完成系统功能。

图4所示是一种基于AD9959芯片的雷达中频信号模拟系统的三通道设计结构框图。其信号模拟过程为:嵌入式PC首先对目标及环境进行建模和运算,以生成雷达信号仿真数据库,然后由DSP根据嵌人式PC传来的目标信息,计算出与DDS在不同时刻需要生成的对应信号频率、相位和幅度数据。并将数据传人FPGA,再由FPGA对数据进行并串转换,并在同步定时脉冲的触发下,在特定时间将数据串行写入DDS,从而完成对DDS的设置。最后再由DDS同时产生三路中频模拟信号。

6 结束语

AD9959由于内部集成有多个DDS通道,它无需多片单通道DDS芯片及其外部电路,因而有助于简化系统设计过程,减小PCB面积。实际试验结果证明:AD9959具有的高性能,可使之广泛的应用于雷达和通信系统之中。本站还有AD9959的配置程序和应用电路,请搜索。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)