用于实时控制系统的嵌入式系统经常需要对模拟量进行测量,通常的方法是以MCU为主产生采集控制时序控制模数转换器,并通过中断或查询的方式读取转换后的结果。由MCU产生采集控制时序将占用较多的系统软硬件资源。而在一般复杂的多路信号测控系统中,MCU需要进行数据存储,通讯,数据处理等多项工作,如果再需要其频繁地产生模数转换控制器的控制时序,将会影响系统的性能,严重时将会成为系统的瓶颈。本文采用CPLD产生A/D转换器的控制时序,使得CPLD主要实现A/D时序控制的功能,DSP主要实现闭环控制算法的功能。

1 系统总体结构

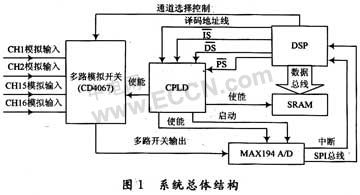

系统以DSP和CPLD为核心,模拟信号从模拟多路开关CD4067接人,利用CPLD进行使能其输入。使用DSP的GPIO口作为模拟多路开关的通道号的选择。A/D转换器使用MAXIM公司的MAX194,其控制时序由CPLD产生。当A/D转换结束后,将会产生一个EOC信号,该信号作为LF2407的外部中断,当DSP接收到该转换结束信号,进入相应的外部中断程序,使用SPI总线来接收A/D转换的数字值,并进行相应的处理。系统的总体结构图如图1所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)