静电放电(ESD)会给电子器件环境会带来破坏性的后果。事实上,在各种各样电路的电路封装和经过装配、正在使用大电子器件中,超过25%的半导体芯片损坏归咎于ESD。

通常情况下,来自人体某个部分(手指)的放电将给给不同的材料充电,随后传递到附着在电子器件的导电触点。这将造成IC损坏,并有理由指责终端用户器件制造商。

这个问题非常严重,以至于欧盟(European Union)已经为任何在经济区销售的商品制定了特殊的ESD抑制标准。现在设计工程师必须为当今更敏感的半导体提供有效的ESD保护。

不幸地是,这项任务经常遵循事后回想的设计原则:首先搭建没有额外过压瞬间抑制的电路,依靠板上的IC来进行保护。如果测试能显示在原型阶段的灵敏度,那么就加上保护器件。如果这种方法被采用来满足当今更低放大电压,增加频率和更低噪声的要求的话,整个设计必须最优的并是集成的。在末端增加保护可能非常昂贵,或由于时间限制而不切实际。

通常,ESD事件是由根据充电过程类型和瞬态电泳严重程度的三种主要ESD算法描述的:人体模型(HBM)、充电器件模型(CDM)和机器模型(MM)。这些模型定义了瞬变效应的类型,因此设计工程师们就可以定义明确的半导体过压芯片瞬变等级灵敏度,以及芯片及装配产品测试规程。利用这些模型,电路设计工程师可以测试芯片和产品的ESD保护效率相一致,而且可以定量地与可选方案进行比较。

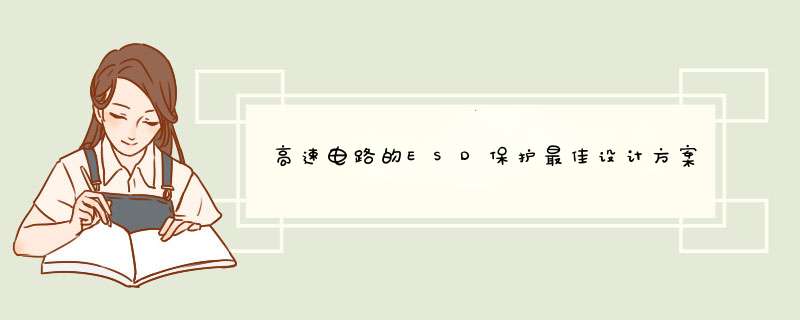

电荷通过一系列电阻器直接传递,例如人的手指,是最普遍的ESD损坏原因。因此,优秀的ESD模型是HBM。在测试中待测器件中(DUT),这是由一个100pF的电容通过一个1500Ω的电阻向器件放电来表示的。这个标准的商业版本是军用规范883方法3015(图1a)。

最流行的HBM变种是国际电工委员会IEC1000-4-2标准,定义为150pF电容通过一个330Ω电阻放电(图1b)。这是欧盟对在其区域内商品销售所必须的国际测试。

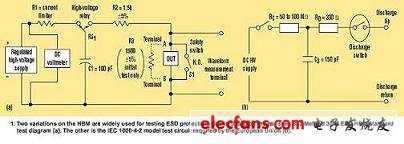

但是,明显的瞬间电压威胁和能量等级的不同存在于两个模型之中。于是设计工程师可以使测试过程适合他们所期望的具体应用。例如,IEC1000-4-2具有一个非常快速的电平脉冲上升时间,能应用更多的脉冲和更高的峰值电流(见表格)。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)