半导体制程之薄膜沉积

在半导体组件工业中,为了对所使用的材料赋与某种特性,在材料表面上常以各种方法形成被膜而加以使用,假如此被膜经由原子层的过程所形成,一般称为薄膜沈积(蒸镀处理)。采用蒸镀处理时,以原子或分子的层次控制蒸镀粒子使其形成被膜,因此可以得到以热平衡状态无法得到的具有特殊构造及功能的被膜。薄膜沈积依据沈积过程中,是否含有化学反应的机制,可以区分为物理气相沈积(Physical Vapor DeposiTIon,简称PVD)通常称为物理蒸镀及化学气相沈积(Chemical Vapor DeposiTIon,简称CVD)通常称为化学蒸镀。以下将分别介绍。

3.1薄膜沈积机制

薄膜的成长是一连串复杂的过程所构成的。图(一)为薄膜成长机制的说明图。图中首先到达基板的原子必须将纵向动量发散,原子才能『吸附』(adsorpTIon)在基板上。这些原子会在基板表面发生形成薄膜所须要的化学反应。所形成的薄膜构成原子会在基板表面作扩散运动,这个现象称为吸附原子的『表面迁徙』(surface migraTIon)。当原子彼此相互碰撞时会结合而形成原子团,此过程称为『成核』(nucleation)。

原子团必须达到一定的大小之后,才能持续不断稳定成长。因此小原子团会倾向彼此聚合以形成一较大的原子团,以调降整体能量。原子团的不断成长会形成『核岛』(island)。核岛之间的缝隙须要填补原子才能使核岛彼此接合而形成整个连续的薄膜。而无法与基板键结的原子则会由基板表面脱离而成为自由原子,这个步骤称为原子的『吸解』(desorption)。PVD与CVD的差别在于:PVD的吸附与吸解是物理性的吸附与吸解作用,而CVD的吸附与吸解则是化学性的吸附与吸解反应。

图(一)薄膜沈积机制 图(一)薄膜沈积机制

3.2物理气相沉积

PVD顾名思义是以物理机制来进行薄膜沈积而不涉及化学反应的制程技术,所谓物理机制是物质的相变化现象,如蒸镀(Evaporation),蒸镀源(镀层的材料来源)由固态转化为气态,溅镀(Sputtering),蒸镀源则由固态转化为电浆(经通电离子化的气体)态。 PVD法是以真空、溅射、离子化、或离子束等法使纯金属挥发,与碳化氢、氮气等气体作用,在加热至400~600℃(1~3小时)的工件表面上,蒸镀碳化物、氮化物、氧化物、硼化物等1~10μm厚之微细粒状晶薄膜,因其蒸镀温度较低,结合性会稍差(无扩散结合作用),且背对金属蒸发源之工件会产生蒸镀不良现象。其优点为蒸镀温度较低,适用于经淬火-高温回火之工、模具。若以回火温度以下之低温蒸镀,其变形量极微,可维持高精密度,蒸镀后不须再加工。

常见的PVD法分为三种:

(一) 蒸镀:在高真空状况下,将所要蒸镀的材料利用热电阻、辐射、电子束或电弧等方式加热达到熔化温度,使原子蒸发,到达并附着在基板表面上。蒸镀时,基材属于基态。

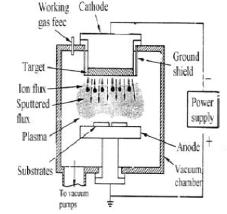

(二) 溅镀:电浆内所产生的部份离子,脱离电浆并往阴极板(靶材)移动,经加速的离子轰撞,在阴电极板的表面除产生二次电子外,还击出电极板原子。 被击出的电极板原子将进入电浆内,且最后传递到另一个放置有芯片的电极板的表面。这些被吸附在芯片表面的吸附原子,将进行薄膜的沈积。

3.2物理气相沉积

PVD顾名思义是以物理机制来进行薄膜沈积而不涉及化学反应的制程技术,所谓物理机制是物质的相变化现象,如蒸镀(Evaporation),蒸镀源(镀层的材料来源)由固态转化为气态,溅镀(Sputtering),蒸镀源则由固态转化为电浆(经通电离子化的气体)态。 PVD法是以真空、溅射、离子化、或离子束等法使纯金属挥发,与碳化氢、氮气等气体作用,在加热至400~600℃(1~3小时)的工件表面上,蒸镀碳化物、氮化物、氧化物、硼化物等1~10μm厚之微细粒状晶薄膜,因其蒸镀温度较低,结合性会稍差(无扩散结合作用),且背对金属蒸发源之工件会产生蒸镀不良现象。其优点为蒸镀温度较低,适用于经淬火-高温回火之工、模具。若以回火温度以下之低温蒸镀,其变形量极微,可维持高精密度,蒸镀后不须再加工。

常见的PVD法分为三种:

(一) 蒸镀:在高真空状况下,将所要蒸镀的材料利用热电阻、辐射、电子束或电弧等方式加热达到熔化温度,使原子蒸发,到达并附着在基板表面上。蒸镀时,基材属于基态。

(二) 溅镀:电浆内所产生的部份离子,脱离电浆并往阴极板(靶材)移动,经加速的离子轰撞,在阴电极板的表面除产生二次电子外,还击出电极板原子。 被击出的电极板原子将进入电浆内,且最后传递到另一个放置有芯片的电极板的表面。这些被吸附在芯片表面的吸附原子,将进行薄膜的沈积。

图(二) 溅镀系统

(三) 离子镀:材料蒸发后,在通往基材的途中经

激发(如离子鎗轰击或辉光放电),使蒸发的原子产生离子化,此经激发的离子化蒸汽原子拥有高能量,能在基材表面产生高附着性,同时也易与通入反应腔的气体发生反应以镀化合物镀层

表(一) 三种PVD法之比较

3.3化学气相沉积

CVD是将反应源以气体形式通入反应腔中,经由氧化还原或与基板反应之方式进行化学反应,其生成物藉内扩散作用而沈积基板表面上。CVD法是将金属氯化物、碳化氢、氮气等气体导入密闭之容器内,在真空、

低压、电浆等气氛状况下把工作加热至1000℃附近2~8小时,将所需之碳化物、氮化物、氧化物、硼化物等柱状晶薄膜沈积在工件表面,膜厚约1~30μm(5~10μm),结合性良好(蒸镀温度高,有扩散结合现象),较复杂之形状及小孔隙都能蒸镀;唯若用于工、模具钢,因其蒸镀温度高于钢料之回火温度,故蒸镀后需重新施予淬火-回火,不适用于具尺寸精密要求之工、模具。图(三)为典型CVD装置图。

化学气相沈积程所包含的主要机制为:(a)首先在沈积室中导入反应气体,以及稀释用的惰性气体所构成的混合气体,『主气流』(mainstream)、(b)主气流中的反应气体原子或分子往内扩散移动通过停滞的『边界层』(boundary layer)而到达基板表面、(c)反应气体原子被『吸附』(adsorbed)在基板上、(d)吸附原子(adatoms)在基板表面迁徙,并且产生薄膜成长所须要的表面化学反应、(e)表面化学反应所产生的气庇生成物被『吸解』(desorbed),并且往外扩散通过边界层而进入主气流中,并由沈积室中被排除。

图(四) 化学气相沈积的五个主要机制

影响薄膜成长的因素有:

(一) 反应炉中的温度与气流:近基板处剧烈的温度梯度(80~120oC/mm)将强烈影响气体的扩散,并造成厚度不

一致或掺杂不均匀。而蒸气压梯度则会与温度梯度造成类似的影响。

图(五) 反应炉内的温度梯度与蒸气压梯度

(二) 基板的预先处理:表面不平整、外来粒子或是污染物都有可能导致薄膜缺陷。一般进行CVD之前,必须先做化学清理:去油(degrease)→氧化(oxidation)→刻蚀(etching)→清洗(rinse)

(三) 基板的方向:基板表面位置的原子、分子密度、几何排列和键结的数量与性质,都会影响薄膜成长。

(四) 蒸镀温度:比起不可逆反应,可逆反应通常需要较高的蒸镀温度。若达到高温限时,可逆反应将会发生气相蚀刻,不可逆反应则会发生过早的沉积。若温度过低而达到低温限,则会有结晶不良且容易被污染的状况。

在集成电路制程中,经常使用的CVD技术有: (一)『大气压化学气相沈积』(atmospheric pressure CVD)系统:在近于大气压的状况下进行化学气相沈积的系统 (二) 『低压化学气相沈积』(low pressure CVD)系统:

LPCVD是在27~270Pa的压力下进行化学气相沈积的,因其生成环境压力低而有此名,由于其生成膜的质量和均匀性好,且成本低,易于实现自动化,因此在半导体集成电路制程工业多采此法。低压化学气相沈积是在炉管中完成的,将气体反应物通入炉管中,反应后形成所需的物质在芯片上。 (三)『电浆增加化学气相沈积』(plasma enhanced CVD)系统:PECVD法中,反应气体从辉光放电等离子场中获得能量,激发并增强化学反应,从而实现化学气相沈积的技术。其中所用的发光放电等离子体属于非平衡等离子体。在此类的等离子体中,自由电子的绝对温度通常比平均气体温度高1到2个数量级,这些高能电子撞击反应物气体分子,使之激发并电离,产生化学性质很活泼的自由基团,并使硅的表面产生更为活泼的表面结构,从而加快了低温下的化学反应。在表(二)中将上述的三种CVD制程间的相对优缺点加以列表比较,并且就CVD制程在集成电路制程中的各种可能的应用加以归纳。

表(二) 各种CVD制程的优缺点比较及其应用

化学与半导体

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)