引言

2003年SoC的收入达到了310亿美元,随着通信行业及个人电子设备市场的快速发展,这一数字有望在2008年再翻上一番。其主要应用领域包括:数字蜂窝式移动电话及基础设施、存储设备、视频游戏机、消费类显示设备、图形卡、数字电视、个人电脑用主板、宽带接入设备以及DVD等。

个人电子设备需求的持续上升表示SoC设计正发展到一个转折点,因为此类系统的产品寿命一般都不会超过一年,而新产品的问世周期为两年。

研究表明,一项高科技新产品只要延迟上市6个月,其生命周期内的收入就要减少大概30%。而且,近年来这种商业影响有愈演愈烈之势,有份报告指出,大容量存储设备推迟三个月上市至少造成了5亿美元的损失。

但是,在过去四年,芯片的一次、二次和三次设计的成功率正在逐步下降,目前,能够实现一次成功的芯片设计还不到总量的39%。虽然功能设计和逻辑设计的错误是导致设计重制的最大影响因素,但电子、物理及光学作用也正对芯片设计起着越来越重要的影响。

本文详尽地描述了三代SoC开发过程中所得到的工程设计结论,举例说明了这些设计方法在设计需求驱动下的持续进步,同时还提出了与最新开发的设计技术同时获得的新结论。

以系统为中心的

全层次设计方法学

基于模块的全层次设计方法学通过同步实现多个VLSI规模的模块设计和顶层设计达到了加快设计进度的目的。

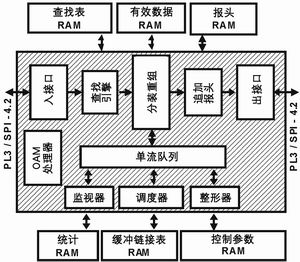

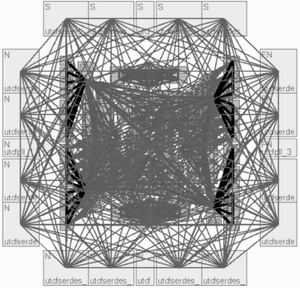

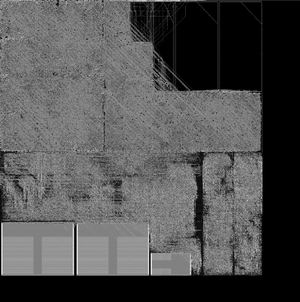

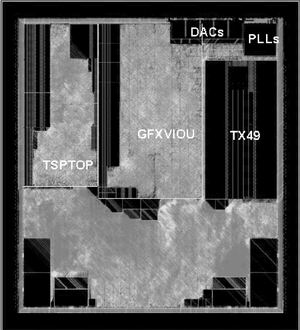

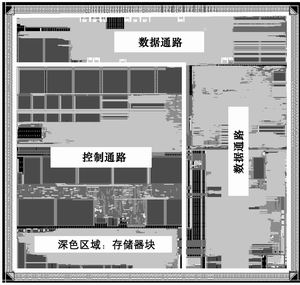

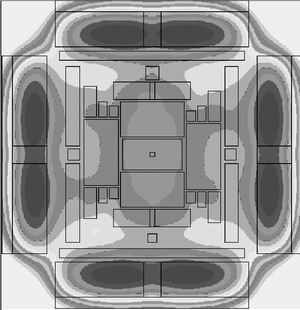

在业内首创的单芯片全双工OC48流量管理器及ATM分装重组(OC48 TM/ATM SAR)SoC的开发期间,从网表到流片的全层次设计方法扩展到整个架构开发以及RTL设计和验证的过程之中(见图1a和1b)。

该方法论延伸了结构/RTL级设计以及电子/物理设计之间的并行性(交错推进),也使得模块设计与顶层设计能够协同进行。该方法包括两个关键的部分:第一,利用定制的FPGA平台来验证RTL设计并开发出“黄金RTL”(GRTL),该平台提供的有效验证吞吐量比起单仿真方法要高出70万倍;第二,GRTL的设计层次在开发过程中保留了下来,架构中同样的模块边界、接口以及同样的GRTL和FPGA分块级扩大了同步设计的范围,进而使硅片设计的时间缩短了一半。

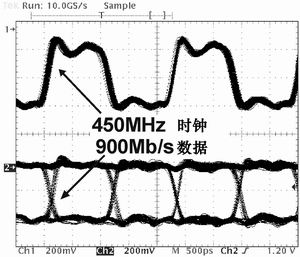

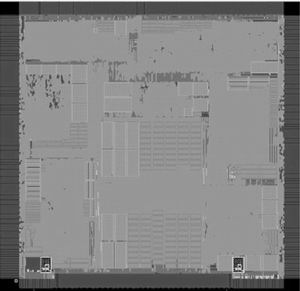

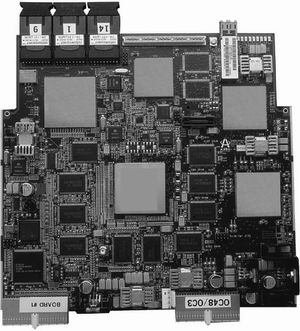

该芯片在8层金属、0.15mm、1.2V的CMOS工艺中集成了大概7800万个(SRAM约占6600万个)晶体管。SPI4.2接口以450MHz DDR运行,有效吞吐量可达900Mb/s。该芯片功率为6W,采用定制设计的1803 FCBGA封装。电路的性能和系统验证电路板如图2a和图2b所示。

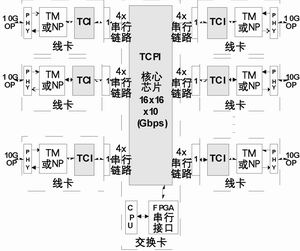

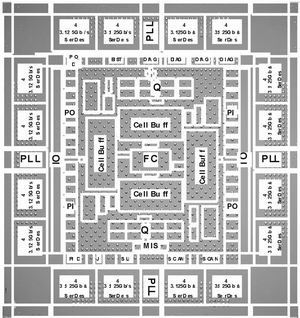

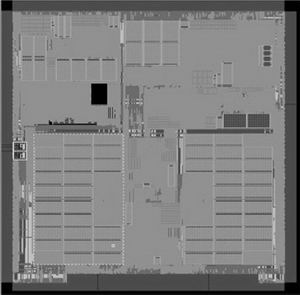

第一款节约成本的、可升级的、160Gb/s的单芯片交换核心(SF:Switch-Fabric)处理器使用了320Gb/s共享存储架构,使效率提高了8倍,并在8层金属、130nm的工艺中集成了3000万个晶体管,64个SerDes端口以及4个3.125GHz的锁相环。

在这个业内首个SoC芯片的开发过程中,同时开发出了基于电路并确保无冲突翻转的三态总线构架,可以把整个顶层布线信号的数量减少3/4如每个三态总线的节点数从5400减少到了1400,使该设计能够在现有的8层金属中实现。

类似于一个圆的独特双轴对称布局规划(见图3)使整个电路的连线总长度最短并使顶层设计的布线堵塞最小化,从而优化顶层布线网络(见图4a),同时该元件的电气功能正确,最大温度梯度为25摄氏度(见图4b)。

本集成电路是一个单芯片中的完整交换板,具有160Gb/s的吞吐量和不高于15W的功耗,并支持10Gb/s到80Gb/s的线路卡。本集成电路使可线性升级的系统的直接设计(straightforward design)具有160Gb/s到1.28Tb/s的吞吐量。图5a和图5b为测量得出的眼图。

该设计方法在数千兆位(MulTI-Gigabit)交换网络系统的130nm芯片(Gb/s SNS IC)的设计与开发过程中得到了进一步改善,同时也开发出新的设计技术,使设计进度加快了28%,电压降(IR drop)减少到20mV以内,时钟扭曲(clock skew)也小于90ps,在超过220万节点的网表中,只需要对其中少于0.1%的的节点进行布线后优化,同时满足了新的片上变化(OCV)、可制造性设计(DFM: design-for-manufacture)和良率设计(DFY: design-for-yield)的要求(见图6a和6b)。

因此,此芯片首次投片就满足了功能设计和电子设计的需求,并在8层金属的130nm低压(LV) CMOS工艺中实现,同时集成了大概7600万个晶体管和高达625MHz DDR的时钟,封装形式为1932 FCBGA封装。

电子/物理设计优化方法

SoC设计中需要考虑的内容包括软/硬件协同设计以及结构/RTL级设计和验证。电子/物理设计需要考虑的内容包括:电源分布,时钟架构和电学特性收敛(electrical convergence),后者还包括时序、片上以及输入/输出信号完整性,OCV、DFM和DFY所涉及的部分也要考虑在内。

顶层模块级物理规划的优化

硅虚拟原型使模块间和模块内的可布线性需求可视化,对优化布局规划起到了直接的作用。此外,基于物理信息的逻辑网表重新综合使得以连线为中心的设计自动化过程进一步得到优化。在OC48 TM/ATM SAR SoC的开发过程中,逻辑综合的优化使电路时序得到了明显改善:布局前时序正确的网表在布线后有1182条冲突路径,最差负间隙(negaTIre slack)为-2ns;而经过逻辑综合优化的网表在布线后只有250条冲突路径,最差负间隙为-0.3ns。

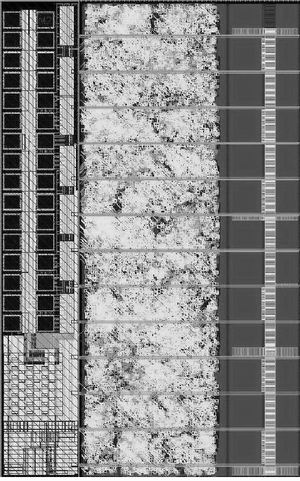

在Gb/s SNS IC的开发过程中, 8个VLSI规模的不同模块连同顶层模块中超过210万个元件被并行设计,包括置入大约500个带有预先设置时序约束的SRAM块,用于预测时序收敛。该方法能够使布局开发和验证、层次化设计以及网表优化在1天内进行3~5次迭代。

接下来对设计模块进行分组和尺寸调整,可以在1天内完成1次完整的设计迭代——从网表到布局后的静态时序分析(STA)再到工程更改单(ECO)的生成。

芯片设计从最终的功能网表到流片能够在大约8周之内完成,与以前的方法相比,该方法能够使进度加快28%。

基于图形的布线技术

新一代基于图形的布线技术已经用于优化最终布线,与自动布线技术的结合能够在信号完整性、可制造性、可布线性以及时序之间进行协同平衡。源自设计试探搜索方法和设计收敛规则的布线规则可用于优化层选择、层排序、平行走线长度缩短、节点屏蔽以及整个布线拓扑。

在Gb/s SNS IC的开发阶段,基于精确的物理连线信息和内置的时序同信号完整性分析引擎,能够同时进行详细布线及连线优化,可使布线后还需要优化的节点数减少到1/10:按照传统布线技术开发的具有约210万个节点的集成电路中一般有不到1%的节点需要布线后优化;而该电路有着220多万个节点,在布线后却只有不到0.1%的节点需要优化。

时钟分布

此类设计一般包含25~40万个触发器,在10~100个物理域中工作,其片上频率为125~626MHz DDR。

时钟树综合可以用于提供对由OCV引起的时钟偏斜的不足控制以及对插入延迟的管理,因此,顶层模块级时钟分布网络拓扑一般能基于每一主模块中的触发器,为该模块定制开发。此类网表一般都不受网表修订的影响,因而加快了设计进度。此外,功率管理、模块级插入延迟、压摆率(slew rate)及相关的时钟偏斜要求能够独立于顶层规划进行优化。

在OC48 TM/ATM SAR SoC中,一个专为优化触发器分布、具有低电阻金属RC延迟的全定制拓扑支持低于1%的占空比变化,并为源同步接口提供小于15ps的时钟偏斜。

在160Gb/s SF SoC中,平衡的时钟拓扑提供了小于60ps的模块内时钟偏斜和小于150ps的顶层最坏情况下的时钟偏斜。顶层带有缓冲链的手工布线可以实现匹配所有域的精确插入延迟。

在Gb/s SNS 集成电路中,最坏情况下顶层模块间的时钟偏斜小于30ps,模块内的时钟偏斜小于90ps。

时序及电子设计

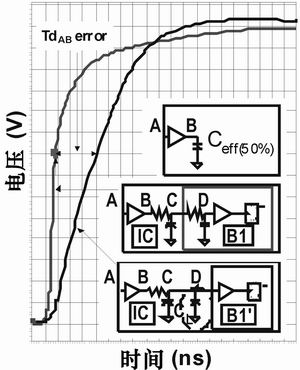

能够反映出边界输入/输出负载及驱动特性的精确“黑盒子”模型对于芯片时序和信号完整性验证至关重要。基于非线性的电流源模型和全分布式耦合RC布线模型的数字延迟计算器可用于计算全芯片路径延迟、实现时序验证并预先考虑信号完整性问题。

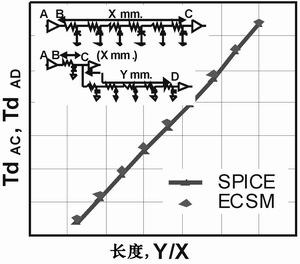

数字的、非线性高效电流源模型(ECSM)用于表征瞬时驱动充/放电流,专为各电路中的每一个输入到输出时序通路而创建,应用于特定节点的RC连线模型中,以计算驱动点和受驱动点双方的信号压摆率和连线延迟(见图7a和7b)。

该技术通过生成和分级传播ECSM模块级模型到顶层来实现全层次时序设计。因此,在计算顶层延迟时能够基于实际的模块前边界条件把设计层次也考虑进去。

延迟计算精确性的提高对设计进度的加快有着直接的影响:在一个包含26万可放置对象和18.7万个节点的小型模块的设计中,相对于全电路仿真,延迟计算的不确定性能够从10%缩减到5%,从而使干扰时序的节点数从2807减少到1512。由于节点数量的减少而消除的不确定通路也就不再需要投入额外的工程设计工作了。

电源分布

M6到M8上符合物理规则的拓扑一般都用于此类集成电路中的电源分布(主要因为这些金属层有着大概低于50%的电阻系数)。

在Gb/s SNS 集成电路中,RDL层中接近60%的布线资源以及M6、M7和M8各层中大概15%的布线资源都用于电源分布。最坏条件下的VDD和VSS IR 压降总共加起来不超过20mV,其中芯片核心部分的VDD为1V,功耗为18W。

电源网络中的IR压降以及电迁移一致性通过对芯片中的电流建模来完成验证,该模型以能精确反映出实际片上电源分布网络情况的阻抗网孔为基础,此类网孔一般都包含3000万到3亿个电阻来保证对电流的精确建模。

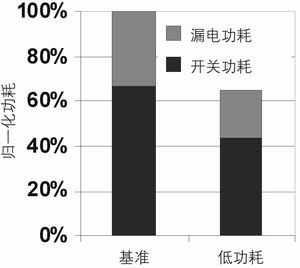

功率管理

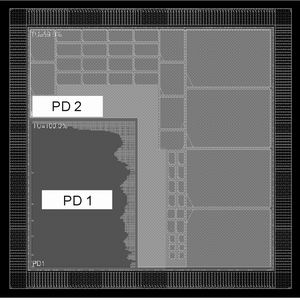

该设计方法论经过扩展,能在自动布局布线模块中支持多个电压域(包括电压接口单元的管理)及多个开启电压电路,可以降低动态功耗和漏电流。在一个包含大概28万个元件(以及额外的SRAM块)、工作频率为300MHz的设计时钟的开发过程中,分析结果表明,该方法可降低42%的功耗(其中输入/输出单元功耗的降低约占50%)(见图8a和8b)。

输入/输出和封装设计

SoC电路一般都有超过200~1000个可同步切换的输入/输出端。通过优化输入/输出电路、总线输入/输出、时钟/控制器输入/输出、VDD/VSS 引脚分配、封装设计以及封装基板设计可以解决输入/输出并发开关噪声效应问题。

对于160Gb/s SF SoC而言,建有14层布线的896脚FCBGA封装可以支持10种不同的VDD 电源布线,向芯片提供约12A的电流。该系统带有1个散热片以及1m/s的空气流,可支持20W的功耗。封装的基板设计考虑了每一个256 Tx/Rx信号(都在3.125Gb/s下运行)的位置,使串扰、布线长度以及阻抗匹配变化最小,同时避免了电迁移问题。

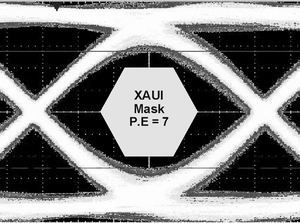

X架构

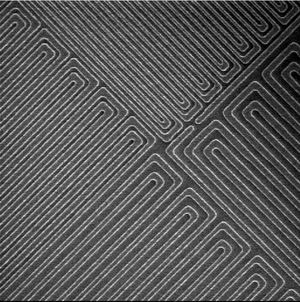

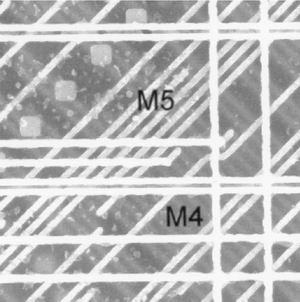

X 架构的主要特征是在中间和顶部金属层全面使用45度布线,能降低芯片内部20%的互连或布线资源。有代表性的X 架构布线如图9a和图9b所示。

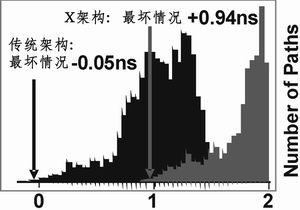

采用X结构的RISC处理器核心的设计使芯片关键路径的延迟缩短了19.8%,芯片面积减小了10%,4个主要模块的连线总长度也分别减少了13%~25%不等,同时通孔数量也相应有28%~37%的减少。这些结果对芯片的性能、功耗、面积以及成本都有着重要影响(见图10a)。

图10b为传统架构同X架构设计的静态时序分析(STA)比较柱状图,使用X架构可将最坏情况下通路延迟间隙(slack)从-50ps增加到+940ps。

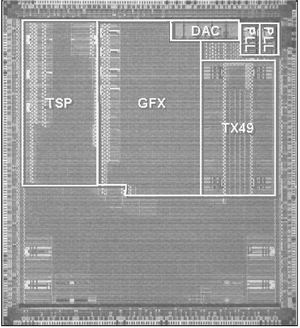

利用X架构的首款商用产品已经实现,该芯片应用于数字电视领域,采用130nm CMOS工艺,集成了270万门电路,工作频率为180MHz。在该设计中,M4和M5为45度布线,借助X架构,使用了层次化设计方法论完成设计,与利用传统技术实现的芯片相比,速度提高了11%,而面积减少了10%(见图11a和11b)。

技术就备

技术就备(Technology Ready)能够在新技术的预测性能与实际性能之间建立起清楚的相关性,有利于实现芯片一次设计成功,并在量产初期得到高的良品率。通过分析实际测试芯片的性能与预测性能之间的差异可促使设计师们采取措施来改进性能。

第一款采用90nm CMOS工艺、含30万门的测试芯片已经制造出来了(见图12)。该设计在5层金属上实现,M3/M4为45度布线,与采用传统技术的设计相比,总连线长度缩短了14%,通孔数也减少了27%。

该方法可用于验证65nm工艺中层和顶层连线中45度布线的可制造性。此类中层连线的线间距(wiring pitch)将在2007年定义为195nm,在2010年减少到135nm,与此同时,顶层连线的线间距将分别定义为290nm和205nm。

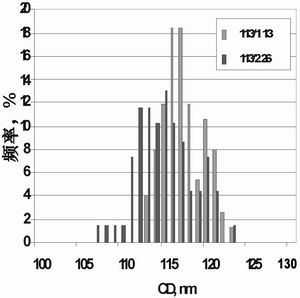

目前,连线线宽/线间距分别为113/113nm和113/226nm的测试芯片都已制造出来。在前一测试环境中,测量均值是117nm,3d极限为+/-7nm,即线宽(CriTIcal Dimension)的6.2%;在后一测试环境中,平均值为115nm,3d极限为+/-10nm,即线宽的8.8%。

在该芯片中,同时采用了传统构架和X构架,采用同样的光学近似修正(OPC)、金属填充(metal fill)、光罩流(mask flow)以及光刻技术,并无需任何特殊的步骤,图形在转弯处以及Z型处有很高的保真度(见图13a和13b)。

结语

本文向读者展示了针对SoC开发的电子/物理设计方法的主要特征,该方法始终都在为实现业内主流SoC的一次设计成功贡献力量,也为及时实现SoC的商业目标同技术目标而推波助澜。■

参考文献

1 Gartner- Worldwide ASIC/ASSP, FPGA/PLD and SLI/SOC App. Forecast, 1Q04

2 Gartner- ASIC and FPGA Suppliers Answer the Call, Jan. 2004

3 A.Khan, "Recent Developments in High-Performance System-on-Chip IC Design," In Proc. IEEE ICICDT, May 2004

4 Collett InternaTIonal Research: 2000, 2002 Functional Verification Studies; 2003 Design Closure Study, Jan. 2004

5 Clark & Wheelwright, "The Product Development Challenge," HBS 1994

6 Craig Matsumoto, "But integration bandwagon not for everyone," EE Times, Oct. 1999

7 A.Khan, et al., "A 150 MHz Graphics Rendering Processor with 256Mb Embedded DRAM," Proc. ISSCC, pp. 150-151, 442, Feb. 2001

8 A.Khan et al., "Design and Development of the First Single-Chip Full-Duplex OC48 Traffic Manager and ATM SAR SoC," CICC, Sep. 03

依次为 图1a-图13a

依次为图1b-图13b

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)