图1 Mediaworks可配置处理器体系的评估结构,用Altera APEX 20K1500 FPGA实现。

提高性能的方法之一是采用常见的小型接口标准,如PCMCIA卡和CF卡,最新的PDA都支持这些接口标准。高级视频和无线处理系统都可以采用PCMCIA和CF电路卡的标准进行开发。为PDA提供优秀流视频产品的最大问题是上述接口标准无法满足高分辨率视频的高数据带宽要求,而视频数据压缩算法可以部分或全部地解决问题。然而,流视频编解码器,如MPEG4是为带宽相对无限的系统开发的,如几个GHz的PC处理,这无法满足市场上大量无线多媒体设备对质量、成本、功耗和性能的需求。因此,加速流视频复杂处理器的视频编解码器的开发成为关键问题。

本文介绍了几种用PDA实现高质量流视频的方法。MediaWorks构建了可配置的媒体处理器,提升了基于可编程逻辑的设计方式,开发出一整套优化的解决方案。采用可配置媒体处理器还可启用软硬件协同设计过程,这对于工程生产效率是非常关键的,能够加快不同性能的视频编解码器的设计开发。

PDA设备都具有观看图形的屏幕和恢复捕获音频的扬声器和麦克风,通常未集成用于视频捕捉的相机。考虑成本关系,多采用最经济的处理器,这些处理器通常不支持双向流视频。因此,需要额外的处理器和压缩/解压硬件和软件。本文试图解决在现有的PDA设备中实现MPEG4视频捕捉、传送和播放的问题。

设计方案中,第一步是增加视频捕捉能力,即利用能以足够的帧速率和图像尺寸工作的传感器开发基于PCMCIA的VGA解析度的相机。虽然绝大部分的PDA无法显示完整的VGA图像,但是可以通过Internet把图像传送给PC用户,就能观看整个图像。选用PCMCIA接口标准很容易开发,也可将Compcat Flash规范作为备用,基本的结构是通过PCMCIA总线把所有图像数据传送给PDA,用软件对输出的图像进行编码,对输入的图像进行解码。

初始结果是每秒7-12帧的帧速率,适合于QCIF(176×144)图像(本地用户看到的图像和正在发送给本地用户的图像)。这些结果证明了这种概念的可行性。但是我们感到,要满足传递图像给PC用户的要求,图像尺寸应该更大一些,帧速率也应该更快一些,使观看起来更流畅。下一代设计中就应该涉及结构的变化来解决上述问题。

因为要在PDA上增加视频功能,需要提供基于PCMCIA/CF的VGA相机。然而,为了增加系统的视频性能,必须解决PCMCIA总线瓶颈和PDA的计算性能限制。设计中通过将视频编码器放置在PCMCIA接口的相机侧来实现这一目标。根据图像序列,编码视频只需要不到未压缩视频流数据速率的十分之一,在接口总线的相机侧编码视频流,允许将更大的视频图像传送给PDA,同时还可传送更多的视频帧。

编码需要部分解码能力,因此视频编码的计算量比解码大。因此用可配置的处理技术为VGA相机开发一个编码器。这种新的视频架构也适用于增加无线功能的下一代产品。视频解码仍在PDA的软件中。

采用这种新的结构,可以得到:

* 每秒30帧的CIF分辨率图像

* 大于每秒20帧的VGA图像

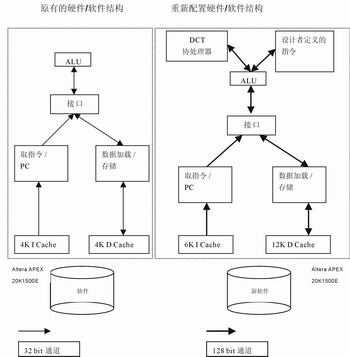

目前的设计方式是寻找最符合任务需求的处理器,但采用诸如Altera的Nios或Tensilica的Xtensa等可配置处理器,能够根据特定的任务定制处理器。采用可配置处理器的设计有以下几步:第一,用APEX 20KE FPGA开发系统或指令集仿真器评估初始的软件和硬件配置,通过分析结果确定性能瓶颈。用硬件、软件或二者结合的方案解决目前最大瓶颈的方法理论上已经通过,正在不断改进。方案已经实现(参数化指令,处理器配置变化,协处理器,新体系等等),正在对结果进行评估。评估结果应证实性能的改进情况。评估;提出方案;通过进一步的评估验证方案,这样周而复始直到硬件/软件方案满足性能要求为止,如图1所示。经过此过程,可能还有一些不可避免的瓶颈,但会逐渐达到最佳点。

可配置处理器方案必须具备以下条件:

* 处理器具有参数化指令集。

* 处理器具有可改变的部件如缓冲尺寸等。

* 处理器具有外部或特定的协处理器。

* 处理器能够在多处理器条件下运行。

* 以上条件的组合。

采用参数化指令处理,开发者可以用基本的处理器配置评估代码,发现瓶颈。常见的瓶颈是缺少高速缓冲。用可配置处理器,开发者能够回退和重新配置处理器,提供更多的指令或数据缓冲,或从2路到3路到4路组合指令。另一类瓶颈是过窄的数据通道限制了一块或大量像素块的编码效率。采用可配置处理器,可以拓宽数据通道,一次对整行像素进行处理,从而节省处理器周期。可以创建特定的指令,以便充分利用这个更宽的数据通道。以MPEG4 *** 作为例,能够定制绝对差值之和(SAD)的计算,这样16个独立的8位像素求和可以用一个所有16像素值的128位同时求和指令替代。

还可以为离散余弦变换(DCT)定制指令,但用专用协处理器可能会更好。采用专用的协处理器,流水线DCT协处理器能够胜任这种工作。软件DCT很容易就占用15%到20%的处理器周期。如果处理器没有所需的带宽,可以用60到80MHz速率的硬件替代DCT软件。

多处理器设计方案类似于使用专用协处理器。因为每帧要量化或模拟化,所以视频编码和解码具有串行特性。DCT或逆DCT(iDCT)顺序对每帧进行处理,因此一帧可以从一个处理器传送到下一个处理器,每个处理器执行特定的功能。因此,整个的帧速率为最慢的处理器的帧速率。采用这种方案,处理器流水线的初始启动会有延迟,原有的编码/解码软件需要重新设计结构并行 *** 作。

以上设计方案的初步结果说明处理周期有明显改善,但还需要进一步优化(分布式数字DCT,重新设计结构,减少中间存储等)。

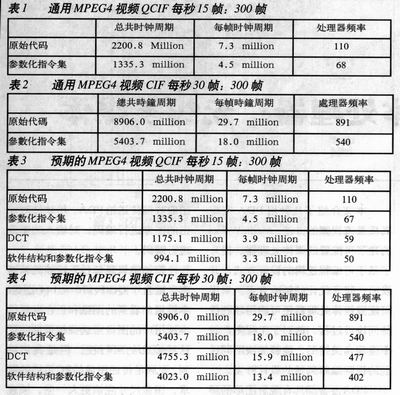

目前的结果归纳于表1至表4中。

一旦确定了最终设计方案,就可以把方案移植到ASIC,或从FPGA设计转换为Altera HardCopy器件,可以降低成本。

本文简要探讨了用可配置媒体处理器解决如何为现有的PDA重新配备多媒体功能,其中的关键是硬件/软件协同设计。在为消除性能瓶颈开发解决方案时,设计者需要在可能的硬件和软件方案之间进行权衡取舍。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)