LSI封装的市场动向

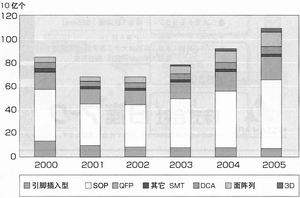

世界电子信息设备市场,按LSI封装形式加以归纳,如图1所示,总交货量在2003年转向增大,其后顺逐增加,到2005年预料将达到2001年的1.5倍的规模。

从封装形式看,以SOP(小外型封装)和QFP(四边扁平封装)为代表的表面贴装居于主流,占压倒的比例,此趋势在2005年也几乎不变。从增长率看,2005年预料将比2001年上升50%。

与之相对,DIP(双列直插式封装)为代表的引脚插入型封装在2002年只占总量的10%,但逐渐减少的趋势一直持续,到2005年将缩小到6%左右。而另一方面,以BGA(球栅阵列)或CSP(芯片尺寸封装)为代表的面阵列封装在2002年以后显示了较大的增长率,到2005年将为2001年的3倍规模,达到所有封装10%以上的占有率。

除上述外,预料有显著增长的将是3D形式的SiP封装(系统封装)。在2001年时几乎还是出不来统计数字的程度,但2005年将达到2001年5倍的规模,比例占到整个封装的3%以上。

图1 多种封装形式需求量变化与预测

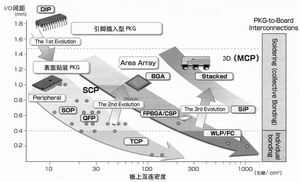

图2 LSI封装形式的变化

LSI封装的技术演进

总体分析

系统产品热电性能不断提升,特别是高频高引脚数的需求,促使封装技术从传统的周边引脚封装走向面阵列封装,也就是引脚插入型进展到表面贴装,而后从SCP(单芯片封装)进展到SiP。新的封装形式问世,但并不意味着过去的封装便马上被取代而消失了,在相当一段时间内,仍是过去的封装形式占据主流。即使今天,周边引脚封装的SOP及QFP仍占大多数。各种封装形式在技术上的变化示于图2。

早期的DIP封装引脚位于IC的两侧,多用于引脚数在64只以下的器件,包括各种存储器和微控制器。之后的表面贴装又分为引脚在IC两侧的SOP和引脚分布在IC四周的LCC(有引线/无引线芯片载体)和QFP形式。SOP用于引脚数在64只以下的器件,包括TSOP(薄型小外型封装)、TSSOP(薄型微缩小外型封装)、SSOP(微缩小外型封装)、SOJ(小外型J型引脚)等。QFP常用于ASIC、逻辑IC与各种中低端器件的高引脚数封装,引脚数范围为36-208和212-304。

为配合IC引脚数越来越多以及器件体积走向轻薄短小的趋势,1990年代之后开始发展以锡球连接芯片与电路板的BGA封装形式,并进一步发展出FPBGA(微细间距BGA)、CSP、FCP(倒装芯片封装)、WLP(晶圆级封装)、TCP(卷带式封装),以及结合多种封装技术将多颗晶片结合在一起的MCP(多芯片封装)、SiP等高端封装技术,以满足CPU、PC芯片组、绘图芯片、FPGA、ASIC芯片的高效能、高速、高集成度、高数、环保、省电等需求。

BGA封装适用于高引脚数IC产品,主要为SoC、绘图芯片组、FPGA、无线通信等应用芯片,尤其I/O数超过300,传统的引脚插入型封装方式已经无法满足需求, BGA封装市场因而日渐扩大。

CSP适用于低引脚数IC,封装后的IC面积比裸芯片大小不超过1.2倍,CSP的优点在于小型与薄型,可提供良好的散热性,主要用于DRAM、SRAM、Flash等存储器产品。尤其是SDRAM延伸出来的新器件DDRⅡ超向高速,体积小,高容量发展,以CSP为标准封装形式,传统的TSOP封装已无法支持其基本架构,必须向CSP转型。

三大技术趋势

Flip Chip技术为典型的晶圆级封装,以芯片凸块(bump)与基板(substrate)连接而取代打线接合(wire bonding)技术,适合I/O数在1000以上的产品,其优势在于能大幅提高产品的电性和散热效能。Flip Chip适合高引脚数、高速、多功能的器件,如具备通信、上网、无线传输、数字图象处理、GPS功能的高效能MCU、MPU、ASIC、RF、高端DSP、SoC、绘图芯片组等,应用层面十分广泛。但其进入门槛高,技术胜出者才能占尽市场优势。

传统IC封装制程是先将晶圆切割成裸芯片,再进行测封,而WLP简化了上述流程,直接在整个晶圆上进行封装和测试之后,再切割成单颗晶粒 ,中间不再需要经过任何封装步骤,明显缩小了IC尺寸,亦大幅降低了封装成本。WLP的优点还在于:由于芯片与电路板间只隔着焊球,因此可缩短电路传输路径,降低了电感与电容,故可有效减少电流损耗与电磁波干扰发生的机率,进而提高电路的工作效率;由于少了IC外部密封的塑胶或陶瓷包装,故IC芯片工作时所产生的热损耗,可直接从芯片背部以热传导与热辐射的方式发散,可有效解决移动电子装置的散热问题。目前便携式电子产品如移动电话、PDA、笔记本电脑、数码相机与MP3播放器等,皆受惠于WLP技术。应用主要集中在三个领域,亦即低I/O数IC(如模拟、射频、功放、电源器件)、存储器(EEPROM 、Flash)与无源元件。未来市场发展除了低引脚数器件持续增加外,存储器等高速器件的应用也将会不断发展。

SoC现阶段的发展面临瓶颈与挑战,如 0.13微米的光罩费用就高达100万美元以上,另一方面制程间距越缩小,栅极漏电流越大,再者细微化后亦造成高速化困难。SiP由于封装中各个元件间仍维持独立,因此可避免遇到SoC设计中模拟与数字电路集成后制程上的困难,并降低电路设计的复杂度,缩短设计时间,并可确保良品率。因此在SoC技术尚未成熟之际,SiP有良好的发展机会,将成为许多系统厂商的首选。

过去的SiP技术,仍以将组合成系统的多个裸芯片放在同一个基板平面上的2D形式为主,而将IC与基板连接的方式,则有打线、倒装以及卷带自动接合(Tape Automated Bonding,TAB)等等技术,此种封装形式仍有电路传输路径过长,封装体积太大的种种缺点。之前的MCM(多芯片模块)封装即是一个2D平面形式的SiP案例。MCM是将多个IC放置于同一个基板平面上、再以打线互相连接。但此种封装形式除了以上传输路径长,封装体积难以缩小的缺点之外,在良品率的控制上也有困难,为了改善上述缺点,目前SiP以逐渐朝向将芯片以3D形式堆叠封装的趋势发展。3D堆叠封装分为两种,一是直接先堆叠裸芯片并连接于基板后,再进行封装(chip stacked),另一种则是将多个封装好的芯片堆叠之后再组合到一起(package stacked)。前者的封装方式,最多只能重叠四层裸芯片,而且在测试上有其难度,目前3D形式的SiP仍是以后者的package stacked为主,不但拥有可预先测试的优点,可堆叠的层数也较多,而且可满足轻薄短小的需求。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)