引言

随着Internet的迅猛发展和各种无线业务需求的增加,目前以承载单一话音业务为主的无线通信网已经越来越不适应人们的需要,所以,以大容量、高数据率和承载多媒体业务为目的的第三代移动通信系统(IMT-2000)成为无线通信的发展方向。码分多址(CDMA)技术凭借其良好的抗噪性、保密性和低功率等优点成为第三代移动通信中最主要的多址接入技术。

和传统的CDMA系统相比,第三代移动通信的最大特点在于能支持多种速率的业务,从话音到分组数据到多媒体业务,并能根据具体的业务需要,提供必要的带宽。3GPP协议规定WCDMA系统支持的业务类型包括:5.15Kbps~12.2Kbps话音数据、 64Kbps电路数据、144Kbps分组数据和384Kbps分组数据。然而,对不同速率业务的基带处理,所需的存储量、运算量以及处理延时差异很大。因此,采用何种硬件结构能有效地处理各种业务是本文所要探讨的问题。

本文首先介绍WCDMA系统的无线信道的基带发送方案,说明其对多媒体业务的支持以及实现的复杂性。然后,从硬件实现角度,进行了DSP和FPGA的性能比较,提出DSP+FPGA基带发送的实现方案,并以基站分系统(BTS)的发送单元为例,具体给出了该实现方案在下行无线信道基带发送单元中的应用。

WCDMA基带发送方案

WCDMA系统的发送单元实现无线信道的基带数据处理(CRC校验、纠错编码、速率适配、交织、复用、成帧)、扩频加扰、合路与功率控制、成型滤波、D/A转换、最后提供给模拟前端。下面以下行链路为例,分别给出基带数据处理方案和扩频加扰调制方案。

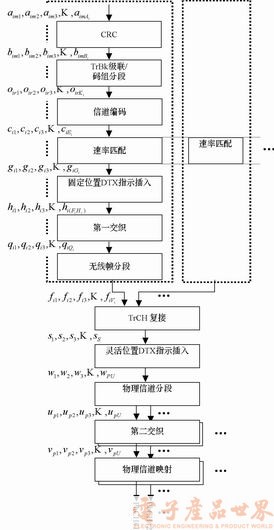

在基带处理流程中(如图1所示),每个传输信道(TrCH)对应一个业务,由于各种业务对时延的要求不同,所以其发送时间间隔(TTI)是不同的(TTI∈{10ms,20ms,40ms,80ms})。具体步骤如下:

首先将各传输信道的一个发送时间间隔(TTI)内的输入数据划分成各传输块,并在每块末尾加上CRC校验比特位,以便收端进行差错检测。

其次将加上校验位后的所有传输块串行级联起来。如果级联后的数据量大于规定的最大编码块尺寸,则需对级连后的数据块进行分段处理,分成若干个尺寸相同编码块,使每个编码块的尺寸小于或等于最大编码块尺寸。对于不同的编码方式,最大编码块尺寸不同。其中,卷积编码: Z = 504;Turbo编码: Z = 5114(Z表示最大编码块尺寸)。

WCDMA所采用的纠错编码有两种:Turbo码和卷积码。无线信道编码是为了接收机能够检测和纠正由于传输媒介带来的信号误差,同时在原数据流中加入了冗余信息,提高了数据传输速率。卷积编码与Turbo编码相比,前者具有译码速度快,时延小等优点;但对较高速率的信道,在满足相同QoS的条件下,后者对信噪比的要求更低。对于数据量小,要求实时性高的业务采用卷积编码,如语音业务;而对数据量大,实时性要求不高的业务采用Turbo编码,如IP业务,多媒体业务。

为了将传输信道的数据适配到物理信道上去,要对编码后的数据流进行速率适配。速率适配是将传输信道上的数据按比特重复或凿去,使得即使不同传输间隔上数据比特数不同,经过传输信道复接后的总数据比特数对于给定的物理信道总是不变的。

在数据块的基带处理过程中有两次交织 *** 作,即第一次交织和第二次交织。交织的作用是将原始数据序列打乱,使得交织前后数据序列的相关性减弱,提高系统对突发性错误的抗干扰能力。两次交织均采用列间交织模式,即先将数据逐行写入矩形阵列中去,再按一定的列交织模式逐列读出。

一个传输信道与一种业务类型相对应,在物理层,有时需要将不同的业务数据复接在一起,通过一个物理信道进行传输,这个过程就是物理层的业务复接。

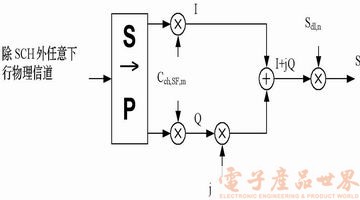

物理信道的扩频由两步组成。第一步是信道化,即将每个数据符号转化为多个码片, 以增加信号的带宽。每个数据符号内的码片数被称做扩频因子(SF);第二步为加扰,由此给扩频信号加扰。在下行链路中,两个连续符号组成的符号对经过串并变换,映射到I和Q支路上。映射的结果是偶数号和奇数号的符号分别映射到I和Q支路上。I 和 Q 支路由相同的实值信道化码Cch,SF,m扩频到码片速率,然后将I和Q支路上实值的码片序列变换成复值码片序列。该序列由复值的扰码Sdl,n加扰(复数相乘)。具体的扩频加扰框图(如图2所示)。

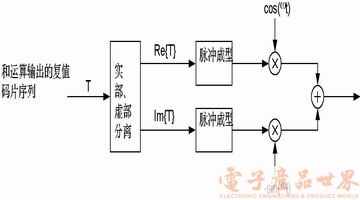

调制信号的码片速率为3.84 Mcps ,扩频过程产生的复值码片序列的调制为QPSK,具体的调制框图(如图3所示)。

图 1 下行传输信道复用结构

图 2 除SCH外所有下行物理信道的扩频

图3 下行链路调制

实现方案

基带数据处理的电路结构

本文提出了“DSP+FPGA线性流水阵列结构”的实现方案:使用DSP与大规模FPGA协同处理基带发送数据。该处理单元以DPS芯片为核心,构造一个小的DSP系统,电路结构如图4所示。

在基带处理单元中,低层的信号预处理算法处理的数据量大,对处理速度的要求高,但运算结构相对比较简单,因而适于用FPGA进行硬件实现,这样能同时兼顾速度及灵活性。相比之下,高层处理算法的特点是所处理的数据量较低层算法少,但算法的控制结构复杂,适于用运算速度高、寻址方式灵活、通信机制强大的DSP芯片来实现。

基带处理单元的需求估计

基带处理单元的需求估计主要包含以下两个方面:

● 各个业务传输通道的数据处理: 以无线信道承载的最高业务速率384Kbps为例进行分析。根据3GPP协议TS25.211,为支持该种速率业务所要求的信道比特速率最大不超过960K(对应扩频增益SF=8,每10ms帧内的比特数是9600bits)。系统在1个10ms帧内所要处理的最大数据量为:

Wmax= 9600bits。

根据3GGP 协议TS 25.212 V2.2.0规定的下行数据基带处理流程(图1所示),并按固定位置复用的方式进行处理,每个数据比特须经过最多10个环节的处理过程,分别是:

估算平均每环节上每比特的处理要求8条指令。则10ms内必须完成的处理指令数是:9600×10×8=768000条。对应的处理能力要求是76.8MIPS。

● 消息处理:包含消息的解释、对应控制参数的计算、发给对应的处理FPGA。估计需求不超过一条承载64Kbps业务的无线信道的基带数据处理的需求。

综合考虑上述两个方面,则整个基带数据处理的等效需求是:

(9600+2400)×10×8/10ms=96MIPS

以TMS320C5410为例,其内部工作时钟频率高达100MHz,运算速度达100MIPS。基于C的软件开发环境和汇编级并行处理的优化程序,优化后的并行执行效率一般为80%,等效的处理能力为80MIPS。可见,若将整个基带数据处理交给该DSP芯片完成,其处理能力无法满足整个处理单元的需求。因此,在基带处理的实现方案中,数据量小的业务,如随路信令,AMR语音业务可由DSP处理;而数据量大的业务,如64Kbps、144Kbps和384Kbps速率的业务,大部分处理环节由FPGA完成。具体实现如下:

● DSP作为主控单元,完成数据提取、消息解析和部分的基带数据处理功能,如第二次交织和成帧等;

● FPGA则在DSP的调度下完成基带数据处理环节中大部分比较耗时的处理功能,如:CRC校验、编码、速率适配等。

在384Kbps业务信道加随路信令的处理中,384bpsK业务数据由DSP通过同步高速接口以DMA方式递交给FPGA,在FPGA中处理;而随路信令因其数据量小,在FPGA处理384Kbps业务数据时,随路信令数据在DSP中同时处理。此方法减少了数据处理时间,提高了处理速度。

结语

本文在分析WCDMA系统因传输不同速率和QoS要求的多种业务而带来的系统复杂度和数据处理延时的基础上,着重介绍了作为一个较好的软硬件结合的设计方案,DSP+FPGA结构在基站分系统的发送单元实现中的具体应用。该硬件电路的实际测试表明,该结构不仅在高速率业务的处理时延上符合规范要求,而且对不同类型的业务处理有较强的适应能力,满足了WCDMA系统对多媒体业务传输的支持。■

参考文献

1. Physical layer-general descripTIon [S].3G TS 25.201 V3.3.0.

2. Physical channels and mapping of transport channels onto physical channels (FDD) [S].3G TS 25.211 V3.5.0.

3. Multiplexing and channel coding [S].3G TS 25.212 V3.5.0.

4. Spreading and modulation [S].3G TS 25.213 V3.4.0.

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)