摘 要:本文介绍了串型级联编码的原理,以及它在数字电视地面传输系统中的应用,通过FPGA设计电路实现编码过程,最后说明串型级联编码的应用优越性。

关键字:FPGA;编码;串型级联编码;数字电视地面传输系统

概述

数字电视地面传输系统是一个无线通信系统。无线信道中,由于环境的影响,以及外来无线信号的干扰,通信质量较有线信道差许多。为了提高系统的抗噪声性能,必须设计合理的信道编译码部分,要求不但可以纠随机错,更重要是可以纠突发错。因为在许多同时出现随机错误和突发错误的复合信道上,往往发生一个错误会波及后面一串数据,导致突发误码超过纠错码的纠错能力。

纠正突发错误的一种有效方法是以一个可以纠正随机错误的码为内码,而以一个纠正突发错误性能良好的码作为外码,构成两级级联的编码方式。内码起到为外码纠正突发错误而清除离散误码的作用,从而提高信道整体纠错能力。本文基于数字电视地面传输系统的基带编码方案来介绍串型级联码的应用。

原理

由信道编码理论可知,随着码长n的增加,译码错误概率以指数方式趋近于零。因此为提高纠错码有效性,就必须使用长码。但码长增加,码率会相应下降,译码设备复杂性与计算量也相应增加,以致难以实现。FORNEY于1966年提出了级联码的概念,有针对性的解决了这一矛盾。该方法将编码过程分为前后串行的几级完成,可以满足信道纠错对编码长度的要求,得到与长码相同的纠错能力和高的编码增益;而且不增加编/译码复杂度。利用级联码,通过合理的构造方法可以达到信道编码定理给出的码限,构造出渐近好码(SHANNON码)。

如图1所示,级联码一般由内码和外码两级组成,内码是GF(2)上的一个[n,k]码,外码是GF(2k)上的[N,K]码,编码规则如下:

(1)先将Kk个二进制信息元划分成K段,每段有k个信息元。

(2)每段的k个信息元可看成是GF(2k)上的一个符号。将K个符号按外码的编码规则编成一个外码,码长为N,有K个信息符号,N-K个校验符号,最小码距为do,码率Ro=K/N。

(3)外码的每一个符号,看成是k个二进制码元的码组,输入内码编码器,得到一个内码,码长为n,有n-k个校验元,最小码距为di,码率Ri=k/n,由此得到N个[n,k]内码的码字序列。两级编码总共得到Nn个二进制码元,Kk个信息元,组成[Nn,Kk,dodi]级联码的码。

由上可知二级级联码是一个[Nn,Kk,dodi]二进制线性分组码,码率R=RoRi。

级联码的译码也对应采用分级处理。先按内码的规则译码,得到N个有k个码元组成的码后,再送入外译码器,最后由外译码器输出的是经过纠错的Kk个信息元。

两级级联编码时,如果信道产生少量的随机错误,通过内码就可以纠错,当产生较长的突发错误或随机错误很多,已经超过内码的纠错能力时,内译码器输出的码子会有少量的几个错误。这仅相当于外码的几个符号错误,所以外码译码器能较容易地纠错。可以看出,级联码用来纠正错误情况严重的组合信道错误非常有效。

级联码的实现中,内码既可以做纯纠错,也可以用做纠错与检错,但一般情况下,级联码被用在组合信道中,内码中的某些码子错误很多,往往超过了内码的纠错能力。所以,内码通常仅用来纠正少量错误,其主要能力用来检错,指出错误位置;纠错任务则由外码译码器完成。这样两级译码的结果,得到了好的纠错效果,还使得内/外译码器均较简单,内译码器是检错译码器,外译码器是纠错译码器。 本质上讲,级联码编码是一种直接序列扩频系统,它把每个外码的码元,用码长为n的内码码子填充,使得系统的带宽扩展,从而提高了系统的抗干扰能力。

FPGA设计

在数字电视地面传输系统中,所用的级联码是外码为RS(204,188)线性分组码,内码为码率可变的(2,1,6)卷积码,交织为卷积交织。

这里只介绍编码器端设计,至于译码端电路,由于译码方法比较多,电路设计不同,不同方案译码性能也有很大差距,这里就不作介绍了。

Reed_Solomen码(简称RS码)是一种多进制的BCH码,在线性分组码中它的纠错能力和编码效率是最高的,所以选择它作为外码。本方案中的RS(204,188,T=16)是RS(255,239,T=16)的截断码。将188字节的数据传送包随机化后,输入编码器,通过RS编码生成16字节的监督元,最后和188字节信息元组成RS码。其码长204字节,可纠8字节长的随机错误或突发错误,每个码元都是有限域GF(256)上的元素。若设m(x)是信息多项式,g(x)是码生成多项式,C(x)是码多项式,整个编码步骤如下。

(1)先用X乘m(x),实际上是把信息码后附加(n-k)个“0”。

(2)再用g(x)除X,得到商Q(x)和余式r(x),即

Xm(x)/g(x)=Q(x)+r(x)/g(x)

(3)编出码多项式C(x)

C(x)=Xm(x)+r(x)

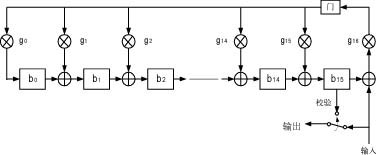

根据其编码步骤,采用有限域除法电路即可实现RS编码,如图2所示。

编码电路的工作过程是,首先对所有寄存器置零,开关接至数据处,此时门连通;然后数据依次送入电路,同时送到输出端;当188字节信息输入完毕后,开关切换至校验端,此时门断开,b0,b1,…,b15里寄存的数据就是所需的校验码元,顺序输出后就得到全部204字节的RS编码码字。

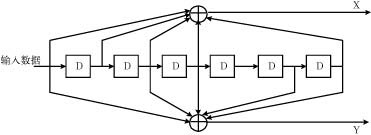

卷积码是一种有记忆的编码,在任意给定的时间单元,编码器的n个输出码字不仅与此时间单元的k个输入有关,而且也与前m个输入有关。目前国际上很多通信系统中首选的标准卷积码为(2,1,6)码,该码能使误码率达到最小,且能克服相位误差。所以在本方案中内码采用(2,1,6)码,子生成元为(171,133)均为8进制。若通过一个凿孔单元对(2,1,6)码删余,还可实现高码率传输,且在提高码率的情况下不增加译码器的复杂性。所以整个电路主要由主卷积编码电路、控制电路和凿孔单元电路构成。主卷积编码实现码率R=1/2的卷积编码,然后用一个凿孔电路按规则要求对输出码字中的特定位置予以删除,以产生较高码率,例如2/3,3/4等码率的卷积码。主卷积码(1/2码率)的实现由6个移位寄存器构成,如图3示。

在两级编码之间,还进行了数据交织,以进一步提高编码抗干扰性能。可以采用分组交织器,通过一个读写地址产生器控制数据按照不同的顺序写入和读出存储器,从而达到数据乱序的目的,交织深度M=102,可以满足使用要求。

结论

在现代通信系统中,信道编码技术已经得到了广泛的应用。编码问题就是在一定的抗干扰能力要求下,合理设计和选择多余度最小码字的问题,也就是如何使可靠性和有效性能够合理兼顾的问题。串型级联编码很好地解决了组合信道错误,使通信系统具有良好的抗干扰能力,短码的利用也提高了传输码率(相对同样纠错效果的长码),串型级联码还有效地控制了信道编码设备的复杂性。

参考文献

1 王新梅,肖国镇.《纠错码原理与方法》.西安电子科技大学出版社,1996

2 Digital Video BroadcasTIng (DVB),1997

3 张鸣瑞,邹世开.《编码理论》.北京航空航天大学出版社,1990

4 邹翊匡镜明,利用FPGA技术实现数字通信中的交织器和解交织器,《电子技术应用》

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)