基于AMBA总线的智能卡控制器设计

摘要:通过分析ISO/IEC 7816-3传输协议,设计该符合协议标准的接触式智能卡控制器,实现对字符传输和块传输这两种不同传输方式的智能卡的支持。该控制器集成于基于AMBA总线的Garfield系列芯片SEP4020中,采用硬件描述语言(verilog)实现。利用EDA工具VCS,Design Compiler对该控制器进行仿真、综合。设计采用Altera公司的FPGA进行验证,并采用SMIC 0.18μm工艺流片成功。在阐述该控制器设计原理的基础上,进行模块划分和具体设计,最后给出仿真、综合和FPGA验证结果。

智能卡(SMART card)通常指一张给定大小的塑料卡片,上面封装了集成电路芯片,用于存储和处理数据。随着嵌入式设备的普及,智能卡在金融、电信、单位考勤、公共事业、交通、医疗等领域得到广泛应用。本文通过对ISO/IEC 7816-3传输协议的分析,基于AMBA总线架构,提出一款智能卡设计方案,通过FPGA验证并采用SMIC 0.18μm工艺流片成功。

2 智能卡控制器工作原理

2.1 复位应答

当控制器检测到智能卡插入 *** 作时对智能卡上电,并按照规范向智能卡发出冷复位信号,智能卡接收到该信号后向控制器发送复位响应,提供编码方式、协议选择、时钟转换因子、波特率调整因子、额外保护时间和最大工作等待时间等参数,后续的会话将按照这些参数进行。如果冷复位之后控制器没有收到符合格式的复位响应,控制器就发出热复位;如果智能卡对热复位仍然没有给出符合格式的复位响应,控制器将结束会话,并释放智能卡。

2.2 传输协议

智能卡控制器有字符传输方式(character transmission)和块传输方式(block transmission)两种传输协议。在字符传输方式中数据以字节单位发送,支持数据奇偶校验。块传输方式以多个字节组成的块为发送单位,发送连续的数据,不支持块中单个字节数据的校验,采用CRC/LRC软件校验。

2.3 基本时间单元ETU

智能卡会话过程中,每个数据位占用时间为1个ETU(Elementary TIme Unit),ETU与智能卡的时钟频率呈线性关系:ETU=F/(D×f)。其中,f为控制器工作频率;F是时钟转换因子;D是波特率调整因子,支持2的次方数和负次方数。F和D的值,可以在智能卡的复位响应后根据响应提供的参数重新设定,如果智能卡没有提供相应的参数,将使用缺省值(F=372,D=1)。

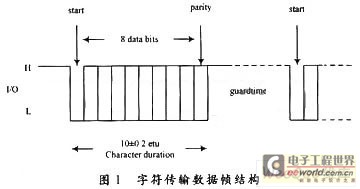

2.4 数据帧

在字符传输方式时,数据帧由10个数据位组成(如图1所示),第一个是起始位(Start),后面跟8 b数据位,最后一个是奇偶校验位。在没有会话的时候,I/O信号线保持高电平。当出现奇偶校验错误时,控制器会重发数据,最多重发4次,如果连续5次都发送不成功,控制器发出中断,请求系统释放智能卡。

在块传输方式时,数据帧由1位起始位和8位数据位构成,没有校验位。块帧由起始域,信息域和终止域构成。起始域3个字节分别为节点地址、协议控制和长度;信息域为待发送的数据,终止域为CRC/LRC校验字节。

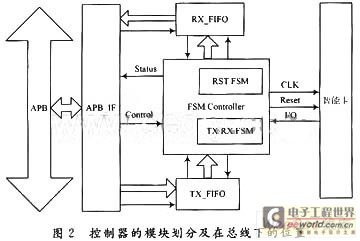

3 模块划分及硬件实现

智能卡控制器包括复位控制模块,收发控制模块,总线接口模块,读缓冲器模块,写缓冲器模块,通过APB接口和AMBA总线相连,对外是CLK,RST,和1根双向的I/O数据线(如图2所示)。

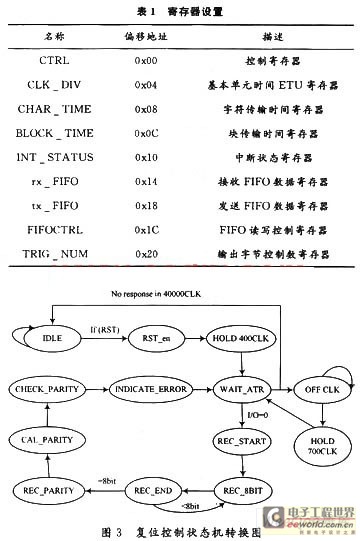

实现各模块功能需设置如下寄存器(如表1所示)。

3.1 复位控制模块

复位控制模块通过状态机的跳变完成对智能卡的复位(如图3所示)。当智能卡上电后,系统初始处于IDLE状态,控制器在使能后按照规范向智能卡发出冷复位信号。首先RST复位信号置低400个CLK以上对卡复位,然后进入等待复位响应状态。控制器经过1 860个CLK后还没有收到复位响应则可以选择进入时钟停止状态。当时钟恢复后,等待700个CLK后重新开始检测复位响应。当I/O数据线上检测到负跳变,则进入起始位接收状态,一个ETU后顺次进入数据接收,校验位接收状态。最后判断校验位正确与否,如果校验正确就保持I/O线为高等待下一个数据的接收;如果出错,则拉低I/O线1个ETU通知智能卡数据出错,请求重传,并设置错误次数计数器。

如果冷复位之后控制器没有收到符合格式的复位响应,控制器就发出热复位,热复位过程同上。如果热复位后40 000个时钟周期内,控制器仍未检测到复位响应,则控制器将结束会话,并释放智能卡。

3.2 数据收发控制模块

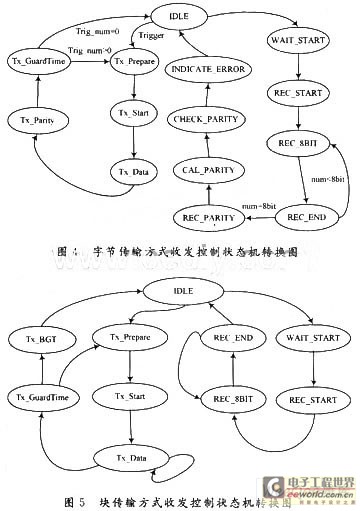

数据收发模块按照系统对控制寄存器,各时间寄存器和输出字节控制寄存器的设置来工作。与复位模块一样,数据收发模块也是由状态机跳变来完成。系统在复位响应完成后进人IDLE状态,根据协议选择字节传输方式(如图4所示)或是块传输方式(如图5所示)。

在字节传输方式下,当系统设置了输出字节控制寄存器后控制器就处于发送状态。首先进入Prepare状态,将发送FIFO中的数据放入移位寄存器,并计算出数据的奇偶校验位,为数据传输做好准备。1个ETU之后进入Start状态,拉低I/O数据线1个ETU来发送数据起始位。接着进入数据发送状态,将移位寄存器中的数据按1 b/ETU的速率串行发出。然后发送1 b奇偶校验位。数据发送完毕后按照系统设置的保护时间将I/O线拉高若干个ETU。最后检测是否已经发出了指定的字节数(Trig_num)。如果数据发送完毕,则跳入IDLE状态等待新的发送设置或转入数据接收;否则进入Prepare状态开始下一个字节的发送。

当系统处于数据接收状态时,首先进入等待起始位状态,在此状态设置超时计数器判断卡是否有响应。当I/O线拉低后就进入接收起始位状态,在该状态的0.5ETU时刻判断I/O数据线是否仍然拉低。如果I/O线跳高则说明是由于I/O线抖动造成的起始位误判,状态跳回等待起始状态;如果I/O线仍然为低,则起始位接收成功,并在0.5个ETU后进入数据接收状态。8 b数据按照1 b/ETU的速率接收,完成后转入接收校验位状态。硬件根据接收的8 b数据计算出校验位并与收到校验位比较,如果不同则I/O线拉低告知智能卡数据错误请求重发,相同则进入IDLE状态等待接收下一个数据或是进入发送状态。

块传输(如图5所示)的接收过程和字符传输类似,按照起始位、8 b数据位的状态机接收数据。一个字节接收完毕后返回IDLE,当没有发送任务时就进入下一次起始位等待。一个字节数据发送完毕后有若干个ETU的保护时间,然后进入Prepare状态准备发送下一个字节数据。当所有数据发送完毕后,系统维持一个块保护时间BGT(Block Guard TIme),然后进入IDLE等待新任务。

3.3 读写数据缓冲器模块

由于APB总线上连接多个功能模块,如USB,UART等都需要占用总线进行数据传输,智能卡控制器只能通过发出总线请求在有限时间占有总线。这使得在进行智能卡读写 *** 作时会申请不到总线从而来不及存储已收到的数据或者来不及获取新的发送数据,增加读写数据缓冲器实现数据暂存可以很好地解决这个问题。缓冲器采用宽度为8位,深度为16的同步FIFO。该FIFO通过在最高位额外设置1 b来判断空/满标志位。当读写指针的8 b数据位和1 b最高位都相同时,FIFO为空。当读写指针的8 b数据位相同并且1 b最高位相反时,FIFO为满。根据FIFO的空满状态来请求或停止新的数据。

3.4 APB总线接口模块

ARM内核通过APB总线读写智能卡控制器,完成了对寄存器的设置、中断状态的读取以及收发数据的读写,读写时序需要符合AMBA APB总线协议。

系统通过总线接口模块设置了控制器工作频率,传输方式、编码方式、时钟转换因子、波特率调整因子。当解析出智能卡为异步半双工字符传输模式时,设置字符发送完毕后的保护时间和最大等待时间。当解析出智能卡为异步半双工块传输模式时,设置块之问保护时间,最大等待之间,以及块内字符间的最大等待时间。系统按照上述设置工作。

系统在设定的参数下完成对接收FIFO的读取和对发送FIFO的写人,并且发出读写使能信号控制FIFO读写。

在收发控制模块产生中断后,对中断状态寄存器设置并交由软件处理。

4 仿真结果及FPGA验证

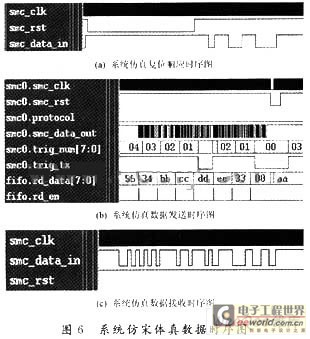

智能卡控制器采用RTL级的Verilog实现,在系统仿真过程中编写智能卡仿真模型。使用Synopsys公司VCS对控制器进行功能仿真和验证。对智能卡的数据收发波形如图6所示。

从仿真结果可以看出,智能卡控制器符合ISO7816-3协议,可以对智能卡进行复位及读写 *** 作。

在FPGA验证中,采用Altera公司的StraTIxⅡ芯片。将智能卡控制器、AMBA总线等模块的RTL代码烧录到ARM开发板的FPGA中,并且将外接一块带有智能卡插槽的扩展板与ARM开发板连接。使用ARM的调试软件ARMulator对控制器进行功能测试。测试结果表明该控制器可以成功完成对智能卡的复位和数据读写 *** 作。

5 结 语

根据上述VCS仿真和FPGA验证的结果,说明该智能卡控制器已经达到功能要求,实现了ISO/IEC7816-3传输协议。利用Design Compiler对该模块进行综合并编写脚本对芯片的面积和时序进行优化,最终逻辑单元为1 368 cells,符合设计目标,实现了对智能卡的数据复位及收发 *** 作。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)