高速USB接口设计

传统的通信方式传输速度慢、抗干扰能力弱、安装麻烦等原因严重阻碍了数据采集设备的发展,随着电子信息技术的迅猛发展。计算机和外围设备得到飞速发展和应用。新一代通用串行总线,简称USB。具有传输线少、速度快、支持热插拔以及易于扩展等优点,很好解决了以上问题,因此串行总线技术在计算机系统及通信设备中得到广泛的应用,为了满足数据采集传输速度的要求.所以提出了高速USB接口的设计与实施。

系统硬件实现数据采集功能,并将采集的数据送至USB控制器,再通过USB接口将数据传送给PC机。硬件设计主要包括USB2.O主控制器(CY7C68013)外围电路设计、CY7C68013与FPGA连接等。系统软件包括USB固件程序、设备的驱动程序和用户界面程序。USB固件程序在keilC中完成,实现对CY7C68013初始化,设备驱动程序为用户界面程序提供软件和硬件平台连接的通道,由DriverStudiO开发;用户界面程序采用VB语言完成,在VB中调用驱动函数中的句柄对硬件设备进行 *** 作,实现数据的接收、保存、显示和打印功能。

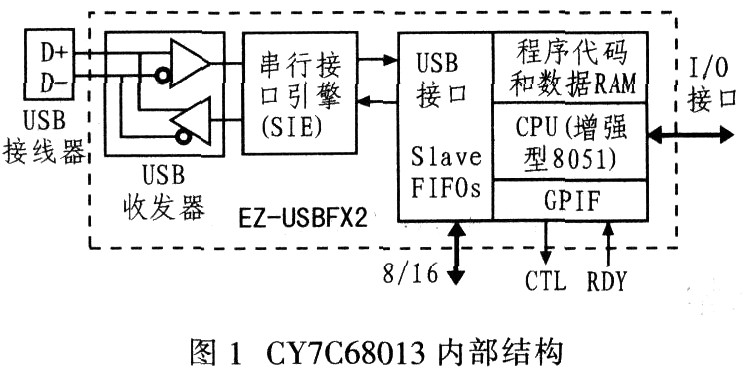

2 USB控制器件CY7C68013内部结构

CY7C68013是Cypres公司生产EZ—USB FX2系列的一种。其内部结构如图1所示。EZ-USB FX2系列的典型应用是无线局域网、移动硬盘、DSL调制解调器等接口类设备。为满足不同用户的需要,Cypress公司为FX2提供了4种封装形式:128引脚TQFP;100引脚QFN;56引脚QFN;56引脚SSOP。这些同种类不同封装的其内部结构相同,不同的封装形式引出的外部引脚数量有所不同。EZ—USB FX2拥有独特的结构,其串行接口引擎(SIE)负责完成诸如数据的编解码、差错控制、位填充等与USB协议有关的功能,将嵌入式MCU(增强型8051)解放出来,简化固件代码的开发。FX2中还包含一个通用可编程接口(GPIF),它支持所有通用的总线标准,并可与外部ASIC、DSP等直接相连,对于EZ—USB FX系列需要微处理器(增强型8051)参与端点FIFO与外围电路之间的数据传输,由于增强型8051本身的工作频率较低,限制了传输速率的进一步提高。虽然这种限制在12Mb/s的全速模式下并不明显,但当速率提升至480 Mb/s的高速模式时,微处理器必将成为整个系统的带宽瓶颈。为此,在EZ—USBFX2中,USB接口和外围电路直接共享FIFO存储器。增强型8051可不参与数据传输,但通过FIFO或RAM的方式访问所传输的数据,这些FIF0与USB之间的传输以数据包的形式实现,此处理被称为“量子FIF0”,它很好的解决了USB高速传输模式下的带宽问题。

EZ-USBFX2内部包含3个固定的64字节端点缓冲区(0xE740~0x7FF)和4KB的可配置端点缓冲区空间(OxF000~OxFFFF)。3个64字节的缓冲区分别用于EPO,EPIIN和EPIOUT,4KB的可配置缓冲区用于EP2、EP4、EP6和EP8。其中,端点0默认为控制端点,其0UT和IN数据共享一块存储空间(OxE740~OxE77F),端点1支持块传输、中断传输和同步传输,其OUT数据占用缓冲区OxE780~0xE7BF,IN数据占用缓冲区OxE7C0~0xE7FFa端点。端点l仅能由EZ-USB FX2的固件访问端点2、端点4,端点6和端点8是大容量高带宽的数据传输端点,其无需8051固件干涉便可同外围电路完成高速数据传输。这4个端点具有非常灵活的配置方式,适应不同场合下的带宽要求。其中双重缓冲意味着USB读写一个缓冲区的同时,另一缓冲区可以与外围电路进行数据通信;三重缓冲增加了第3个数据缓冲区,可供USB端或外围电路端使用;四重缓冲增加了第4个缓冲区。多重缓冲结构可在数据读写双方速度相似时,有效提高USB带宽的性能,平滑带宽抖动,并减少双方的互相等待时间。

3 硬件设计

USB控制器及其外围电路组成系统的数据读取和传输模块,主要负责读取数据及与PC机通信,从而完成系统功能。EZ—USBFX2和FPGA的从SlaveFIF0硬件连接如图2所示。

EZ-USBFX2和FPGA之间的通信模式既可选择从属FIFO接口模式,也可选择GPIF接口模式。通过配置IF—CONFIG[l:0]来选择。当为11时,选择从属FIFO接口模式;当为10时,选择GPIF接口模式。

当EZ—USBFX2被设置为SlaveFIFO接口模式时,USB数据在PC机和FPGA中传输,不需EZ-USBFX2的CPU参与,而经EZ-USBFX2的内部端点FIFO传输。对FPGA端点FIFO提供了FPGA经16位数据总线FD连接EZ—USBFX2 FIFO,其数据总线是双向,通过SLOE引脚控制输出。FIFOADR[1:O]引脚选择4个FIFO中的一个与FD总线连接。异步方式下,SLRD和SLWR是读/写选通信号。同步方式下,SLRD和SLWER作为IFCLIK时钟引脚使能信号。这里采用异步方式。

4 USB固件程序的设计

为了简化固件编程,Cypress提供了固件编程框架,在此基础上只需要修改少量代码即完成固件编程。固件编程框架完成了USB标准设备请求和USB电源管理,并提供了任务调度函数,在任务调度函数中编写少量代码就可完成编程。只需要提供USB设备描述符表和外围 *** 作程序就可实现一

个功能完整的USB设备。

4.1 函数介绍

Void TD_Init(void):此函数主要完成EZ-USBFX2的初始化,在EZ—USBFX2再次枚举和开始任务分配前被调用,其目的是初始化各个端口以及各端口的先入先出缓冲区。

Void TD_PoLL(void):此函数在设备运行时被重复的调用,应包括完成特别任务的代码。在该函数返回前,优先级高的任务可能己完成。若它返回值为假,EZ—USBFX2将不会影响设备请求和USB总线设备挂起事件。若需要大量的处理时间,EZ-USBFX2会通过多次调用TD_PoLL函数将时间分段。

BooL TD_suspend(void):此函数是在设备进入挂起状态前调用,在其中加入适当的代码,配置设备的工作状态,可使设备处于低功耗状态并返回真值。可以改动TD_Suspend的程序代码,使其返回为假,可使EZ-USBFX2不进入挂起状态。

Void TD_Resume (void):当外部要求重新启动时,设备会通过调用此函数对处理器重启,即TD_SUspendO函数的逆 *** 作。此时,设备在正常电源下重新启动。设备请求函数主要完成对来自主机的命令和请求的处理工作。

4.2 固件主程序

fw.c是固件程序的主程序文件,负责处理主机发出的各种USB设备请求。该程序首先初始化所有的内部状态变量,然后调用TD_InitO函数初始化,并打开中断。然后,固件程序开始列举USB设备,直至在端点0上接收到SETUP包为止。一旦接受到令牌包,框架将开始交互的任务调度。

整个系统实现过程中,设置一些重要寄存器。表1列出EZ—USBFX2为异步从属FIFO自动模式时,需要配置的相关寄存器。

5 FPGA程序的设计

编程思路:由于CY7C68013设置为异步SlaveFIFO模式,根据异步FIFO读写状态图,选择状态机来编写进程。其状态图如图3所示。

6 结语

以CY7C68013和FPGA接口为例描述了USB芯片的SlaveFIFO固件程序流程和设计思想,并且在项目中得到了实际应用,并且数据连续传输无误码,无丢失。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)