关键词:PCI总线,数据采集,VHDL,CPLD

1 引 言

数据采集技术是信号处理一个非常重要的环节,广泛应用于雷达、通信、遥测遥感等领域。在研制基于新型连续波噪声雷达体制的新型连续波雷达时,为了研究更加有效灵活的雷达信号处理算法,利用计算机这个通用的计算和控制平台,先将雷达信号采集到计算机上,然后在计算机上进行雷达信号处理算法的研究。课题要求对雷达I和Q两个通道的信号进行采集,采样精度为12位,最高的采样频率为20兆。传统的基于ISA、EISA和VL总线的数据采集,受到总线带宽、控制方式和实现难易程度的制约,不能满足课题要求。而PCI总线以其峰值传输速率高达每秒132兆字节、支持突发传输等突出的性能,成为我们雷达数据采集首选的计算机IO接口。本文介绍了采用PLX9054作为PCI总线接口芯片的大容量雷达数据采集系统的开发,系统包括数据采集卡和配套软件。

2 数据采集卡系统结构的介绍

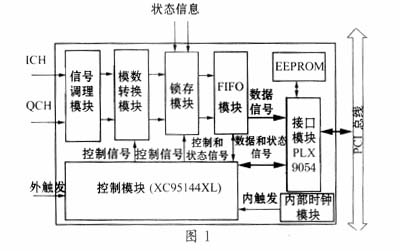

数据采集卡的系统结构如图1所示。雷达输出的I和Q两通道视频信号通过数据采集卡的信号调理模块,经隔离限幅放大后,送到模数转换模块,在这里,两路模拟信号分别被转换成12位的数字信号。两路12位的数字信号经锁存后,被送到FIFO模块缓存起来,这些缓存的数据将通过PCI总线接口模块以DMA方式存入计算机内存。当数据采集完成后,这些内存中的数据将存入硬盘,生成雷达数据文件。每个通道的雷达信号只用了16位中的12位,还有4位未用,我们利用这4位来传输雷达随机二相码码字等一些数字状态信息,这些信息将从锁存模块输入,随雷达信号同步采集到计算机中。

数据采集卡的控制是由控制模块来完成的。内部时钟模块提供内触发信号,它和外触发信号一起接到控制模块,由控制模块根据用户要求来选择使用不同的触发信号。EEPROM内存储有PCI总线接口芯片PLX9054的配置信息。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)